# When Placement Meets GPU: GPU-Accelerated VLSI Placement and Device Placement for GPUs

## LIU, Lixin

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

in

Computer Science and Engineering

The Chinese University of Hong Kong

August 2023

## Thesis Assessment Committee

Professor SHAO Zili (Chair)

Professor YOUNG Fung Yu (Thesis Supervisor)

Professor YU Bei (Committee Member)

Professor LIN Mark Po-Hung (External Examiner)

## **Abstract**

Placement serves as a fundamental yet challenging combinatorial optimization problem in various research areas including but not limited to artificial intelligence, electronic design automation, resource scheduling, etc. With the rapid development of GPU's computational power, GPU acceleration become an important research direction to pursue to handle large-scale problems with parallelism. Motivated by this emerging trend, we exploit the potential of GPU in placement and study two essential problems when placement meets GPU: GPU-accelerated VLSI placement and device placement for GPUs.

VLSI placement is an extremely sophisticated problem in electronic design automation (EDA), that is highly correlated to the circuit's power, performance, and area (PPA). Meanwhile, the enormous number of transistors in modern chips hugely increases the computational complexity of VLSI placement. To address this rising demand for an effective yet scalable VLSI placer, we propose a GPU-accelerated VLSI placement framework that effectively generates high-quality solutions in an extremely fast manner. We also extend the proposed framework with neural network enhancement and illustrate the possibility of incorporating a neural network component into analytical placement. Besides wirelength, routability is another important metric in VLSI placement, which determines whether a solution is routable. A placement with low routability will cause flow failure and affect design closure. To this end, we develop a GPU-accelerated detailed-routability-driven placer, to achieve superior solution quality and remarkable runtime speedup.

As for device placement, it is an essential topic in machine learning system (MLSys) and aims at tackling the scalability problem of training a large-scale deep neural network (DNN)

on a distributed system. Meanwhile, various network topologies emerge today for DNN training acceleration, which greatly challenges the existing device placement heuristics. We propose an efficient device placement framework to maximize the throughput of training a large DNN onto a multi-GPU system with general device topology. We show that our framework speeds up the pipeline training throughput on systems with different GPU topologies and is able to handle the placement problem for heterogeneously interconnected architectures.

# 摘要

佈局在人工智能、電子設計自動化、資源調度等各個研究領域中都是一個基礎且具有挑戰性的組合優化問題。隨著GPU計算能力的快速發展,GPU加速成為並行處理大規模問題的重要研究方向。受到這一新興趨勢的推動,我們發掘GPU在佈局方面的潛能,研究了佈局在與GPU相遇時的兩個關鍵問題:GPU加速的VLSI佈局和面向GPU的設備佈局。

VLSI佈局是電子設計自動化(EDA)中極其復雜的問題,其與電路的功耗、性能和面積(PPA)高度相關。與此同時,現代芯片中龐大的晶體管數量極大地增加了VLSI佈局的計算復雜度。為了滿足現如今對一個高效且可擴展的VLSI佈局器不斷增長的需求,我們提出了一個GPU加速的VLSI佈局框架,該框架可以以極快的速度生成高質量的佈局方案。我們還通過神經網絡增强擴展了所提出的框架,說明了將神經網絡組件用於解析性佈局的可能性。除了線長以外,可佈線性是VLSI佈局中另一個重要指標,它決定了佈局方案是否可以完成佈線。可佈線性較低的佈局會導致設計流程失敗且影響設計收斂。為此,我們開發了GPU加速的面向詳細佈線性的佈局器,其實現了卓越的佈局效果並且顯著提高了運行效率。

至於設備佈局,它是機器學習係統(MLSys)中的一個重要課題。它旨在解決在分佈式係統上訓練大規模深層神經網絡(DNN)時面臨的可擴展性問題。同時,如今出現了各種用於加速DNN訓練的網絡拓撲,這對現有的設備佈局啓發式算法提出了很大的挑戰。對此,我們提出一個高效的設備佈局框架,以最大化在具有通用設備拓撲的多GPU係統上訓練大規模DNN時的吞吐量。我們的框架不僅可以提高在不同GPU拓撲下的流水線訓練吞吐量,而且能夠處理在異構互聯結構下的設備佈局問題。

## Acknowledgments

First of all, I would like to express my sincere gratitude and appreciation to my supervisor, Prof. Evangeline F.Y. Young for her insightful guidance and kind support throughout my Ph.D. journey. I deeply appreciate every meaningful discussion we have had about research and life. I am forever grateful for her warm advice and continuous encouragement.

Besides my supervisor, I also want to express my thanks to the rest of my thesis committee members, Prof. Zili Shao, Prof. Bei Yu and Prof. Mark Po-Hung Lin, for their valuable comments and constructive suggestions.

My sincere thanks also go to all of my colleagues: Dr. Jordan Chak-Wa Pui, Dr. Haocheng Li, Dr. Yuzhe Ma, Dr. Haoyu Yang, Dr. Jingsong Chen, Dr. Bentian Jiang, Dr. Jinwei Liu, Dr. Xiaopeng Zhang, Dr. Dan Zheng, Fangzhou Wang, Wei Li, Zhuolun He, Shiju Lin, Xinshi Zang, Bangqi Fu, Tianji Liu, Qijing Wang, Wing Ho Lau, Qin Luo and Yang Sun. It was a great pleasure working with them at The Chinese University of Hong Kong.

Finally, this thesis would not exist without the support and sacrifice of my family. I am deeply grateful to my parents Feiwu Liu and Yixia Lin for their unconditional love. No matter what challenges I have encountered in life, they are always there for me, offering their best support.

## **Contents**

|                        | Abs          | ract                                             | . iii |

|------------------------|--------------|--------------------------------------------------|-------|

|                        | Ack          | nowledgments                                     | . vi  |

|                        | List         | of Figures                                       | . x   |

|                        | List         | of Tables                                        | xii   |

| 1                      | Intr         | duction                                          | 1     |

|                        | 1.1          | Graphics Processing Unit                         | . 1   |

|                        |              | Placement Problem                                | . 3   |

|                        |              | 1.2.1 VLSI Placement in EDA                      | . 3   |

|                        |              | 1.2.2 Device placement in MLSys                  | . 4   |

|                        | 1.3          | Overview of this Thesis                          | . 6   |

| 2                      | ature Review | 7                                                |       |

|                        | 2.1          | VLSI Placement in EDA                            | . 7   |

|                        |              | 2.1.1 VLSI Placement                             | . 7   |

|                        |              | 2.1.2 Routability Optimization in VLSI Placement | . 11  |

|                        |              | 2.1.3 GPU-Accelerated VLSI Placement             | . 12  |

|                        | 2.2          | Device Placement in MLSys                        | . 14  |

|                        |              | 2.2.1 Data and Model Parallelism                 | . 14  |

|                        |              | 2.2.2 Pipeline Parallelism                       | . 15  |

|                        |              | 2.2.3 Device Placement for GPUs                  | . 16  |

| 3                      | GPU          | -Accelerated VLSI Placement                      | 19    |

|                        | 3.1          | Preliminaries                                    | . 20  |

| 3.2 Overview of Xplace |              | Overview of Xplace                               | . 21  |

|                        | 3.3          | Operator-Level Optimization                      | . 22  |

|                        |              | 3.3.1 Wirelength Operator Combination            | . 22  |

|                        |              | 3.3.2 Density Operator Extraction                | . 23  |

|                        |              | 3.3.3 Operator Reduction                         |       |

|                        |              | 3.3.4 Operator Skipping                          | . 26  |

|                        |              | 3.3.5 Determinism                                | . 27  |

| 3.4 Placement-Stage-Aware Parameters Scheduling |     |                            | nent-Stage-Aware Parameters Scheduling                           | 27 |  |  |

|-------------------------------------------------|-----|----------------------------|------------------------------------------------------------------|----|--|--|

|                                                 | 3.5 | Extend                     | ding Xplace via Neural Enhancement                               | 29 |  |  |

|                                                 | 3.6 | Experi                     | mental Results                                                   | 33 |  |  |

|                                                 |     | 3.6.1                      | Validation on Contest Benchmarks                                 | 34 |  |  |

|                                                 |     | 3.6.2                      | Ablation Studies on Operator-Level Optimization                  | 37 |  |  |

|                                                 |     | 3.6.3                      | The Effectiveness of Determinism Implementation                  | 37 |  |  |

|                                                 |     | 3.6.4                      | Neural-Enhanced Performance                                      | 39 |  |  |

|                                                 | 3.7 | Conclu                     | uding Remarks                                                    | 39 |  |  |

| 4                                               | GPU | J <b>-Accel</b>            | erated Detailed-Routability-Driven VLSI Placement                | 41 |  |  |

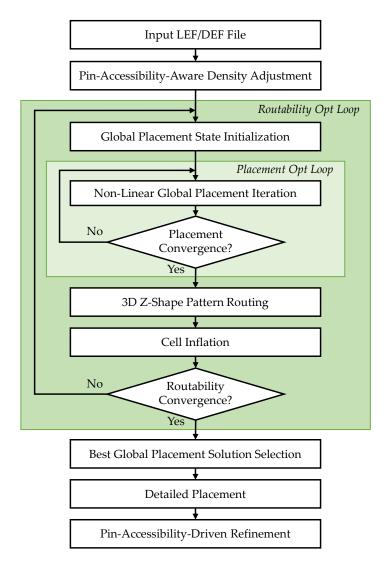

|                                                 | 4.1 | Overv                      | iew of Xplace-Route                                              | 42 |  |  |

|                                                 | 4.2 | Detaile                    | ed-Routability Optimization                                      | 43 |  |  |

|                                                 |     | 4.2.1                      | Pin-Accessibility-Aware Density Adjustment                       | 43 |  |  |

|                                                 |     | 4.2.2                      | Routing Congestion Map                                           | 44 |  |  |

|                                                 |     | 4.2.3                      | Cell Inflation                                                   | 46 |  |  |

|                                                 |     | 4.2.4                      | Placement State Re-initialization                                | 47 |  |  |

|                                                 |     | 4.2.5                      | Solution Selection Criteria                                      | 48 |  |  |

|                                                 |     | 4.2.6                      | Pin-Accessibility-Driven Refinement                              | 52 |  |  |

|                                                 | 4.3 | Experi                     | mental Results                                                   | 52 |  |  |

|                                                 |     | 4.3.1                      | Experimental Settings                                            | 53 |  |  |

|                                                 |     | 4.3.2                      | Quantitative Results                                             | 53 |  |  |

|                                                 |     | 4.3.3                      | Ablation Studies on Detailed-Routability Optimization Techniques | 55 |  |  |

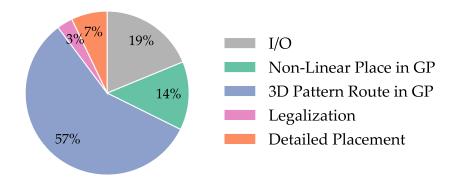

|                                                 |     | 4.3.4                      | Runtime breakdown                                                | 56 |  |  |

|                                                 | 4.4 | Conclu                     | uding Remarks                                                    | 57 |  |  |

| 5                                               | Dev | evice Placement for GPUs 5 |                                                                  |    |  |  |

|                                                 | 5.1 | Motiva                     | ation                                                            | 58 |  |  |

|                                                 | 5.2 | Overv                      | iew of Parmesan                                                  | 62 |  |  |

|                                                 | 5.3 | Opera                      | tor-Level Model Partitioning                                     | 62 |  |  |

|                                                 |     | 5.3.1                      | Dynamic Programming                                              | 63 |  |  |

|                                                 |     | 5.3.2                      | Operator Clustering                                              | 65 |  |  |

|                                                 |     | 5.3.3                      | Iterative Refinement                                             | 67 |  |  |

|                                                 |     | 5.3.4                      | Implementation Details of Operator-Level Model Partitioning      | 68 |  |  |

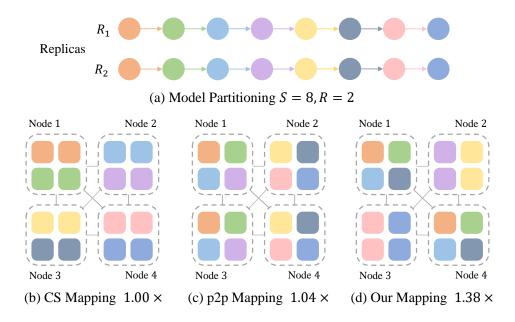

|                                                 | 5.4 | Device                     | Mapping for General Device Topology                              | 70 |  |  |

|                                                 |     | 5.4.1                      | A General and Optimal Searching Algorithm                        | 70 |  |  |

|                                                 |     | 5.4.2                      | Two Instantiations                                               | 71 |  |  |

|                                                 | 5.5 | Discus                     |                                                                  | 74 |  |  |

|                                                 | 5.6 |                            |                                                                  |    |  |  |

|                                                 | 5.7 | -                          | mental Results                                                   | 77 |  |  |

|                      | 5.7.1  | Experimental Settings                         | 78 |  |  |

|----------------------|--------|-----------------------------------------------|----|--|--|

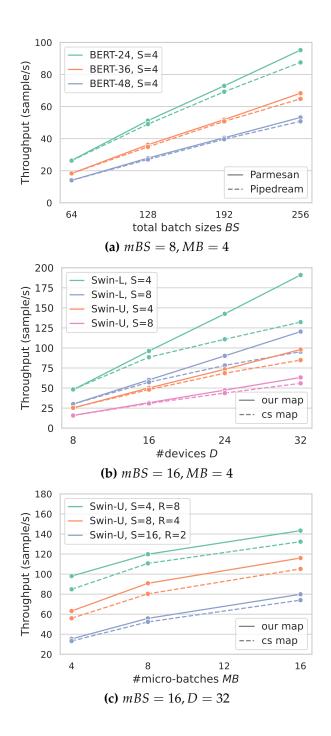

|                      | 5.7.2  | Validation on Different Device Topologies     | 82 |  |  |

|                      | 5.7.3  | Ablation Studies on Model Partitioning        | 87 |  |  |

|                      | 5.7.4  | Impact of Timeout Heuristic of Device Mapping | 89 |  |  |

|                      | 5.7.5  | Comparison to Heuristic Mappings              | 89 |  |  |

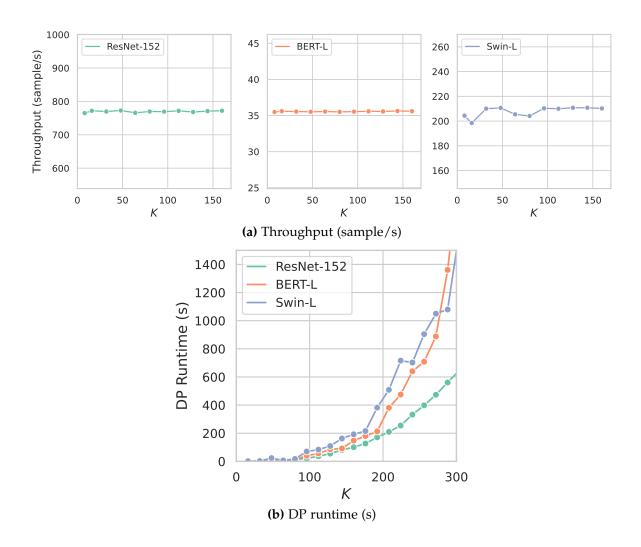

|                      | 5.7.6  | Flow Runtime                                  | 93 |  |  |

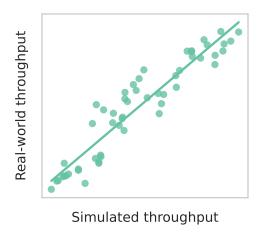

|                      | 5.7.7  | Simulator's Accuracy                          | 94 |  |  |

| 5.8                  | Proofs | 3                                             | 95 |  |  |

|                      | 5.8.1  | Proof of Theorem 1                            | 95 |  |  |

|                      | 5.8.2  | Proof of Theorem 2                            | 95 |  |  |

|                      | 5.8.3  | Proof for Optimality of Algorithm 2           | 95 |  |  |

|                      | 5.8.4  | Proof of Proposition 1                        | 96 |  |  |

|                      | 5.8.5  | Proof of Theorem 3                            | 98 |  |  |

| 5.9                  | Concl  | uding Remarks                                 | 98 |  |  |

| Conclusion           |        |                                               |    |  |  |

| References           |        |                                               |    |  |  |

| List of Publications |        |                                               |    |  |  |

# **List of Figures**

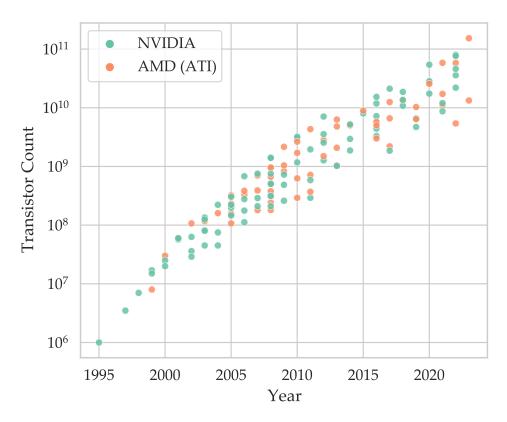

| 1.1 | Transistor count on NVIDIA and AMD (ATI) GPUs                                                | 2  |

|-----|----------------------------------------------------------------------------------------------|----|

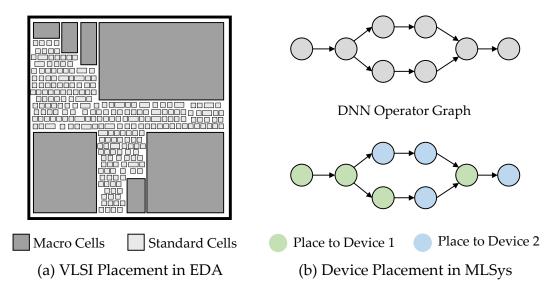

| 1.2 | Illustration for VLSI placement and device placement                                         | 4  |

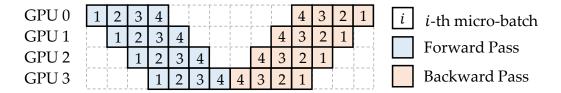

| 2.1 | An example of GPipe's fashion pipeline parallelism                                           | 15 |

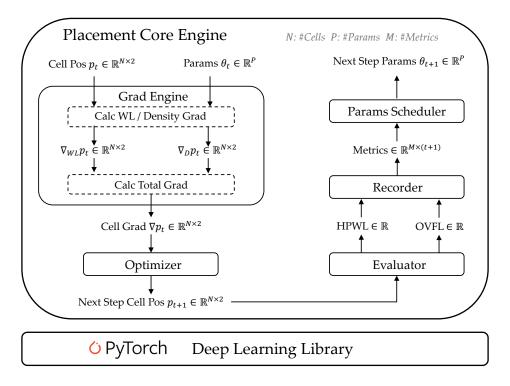

| 3.1 | Overview of Xplace                                                                           | 22 |

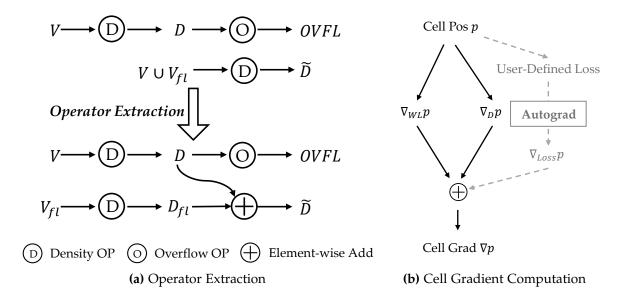

| 3.2 | Illustration for the operator extraction technique and the cell gradient compu-              |    |

|     | tation scheme                                                                                | 25 |

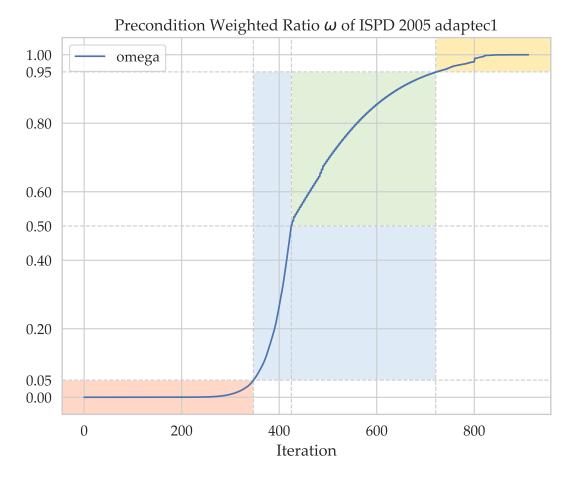

| 3.3 | An example of the precondition weighted ratio $\omega$ of ISPD 2005 <code>adaptec1.</code> . | 28 |

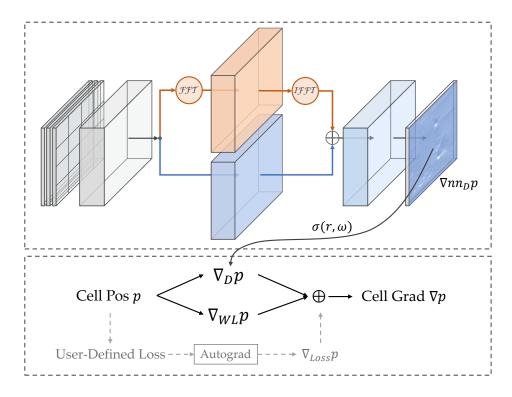

| 3.4 | Neural-network plugged-in placement extension                                                | 31 |

| 4.1 | Routability optimization flow of Xplace-Route                                                | 42 |

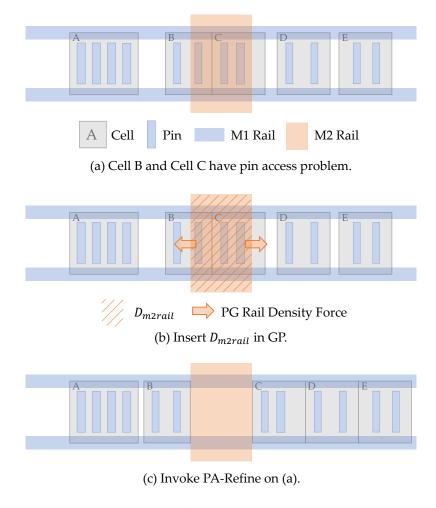

| 4.2 | Pin-accessibility-aware optimization techniques                                              | 44 |

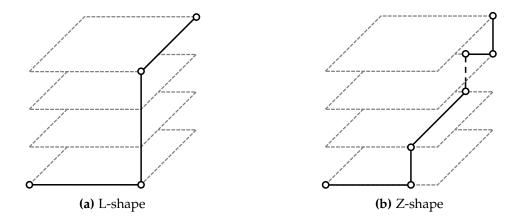

| 4.3 | 3D L-shape and Z-shape pattern routing                                                       | 45 |

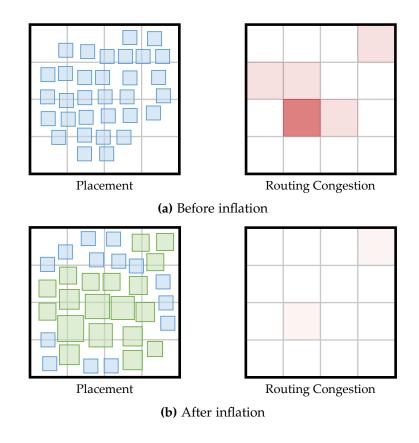

| 4.4 | An example of cell inflation                                                                 | 46 |

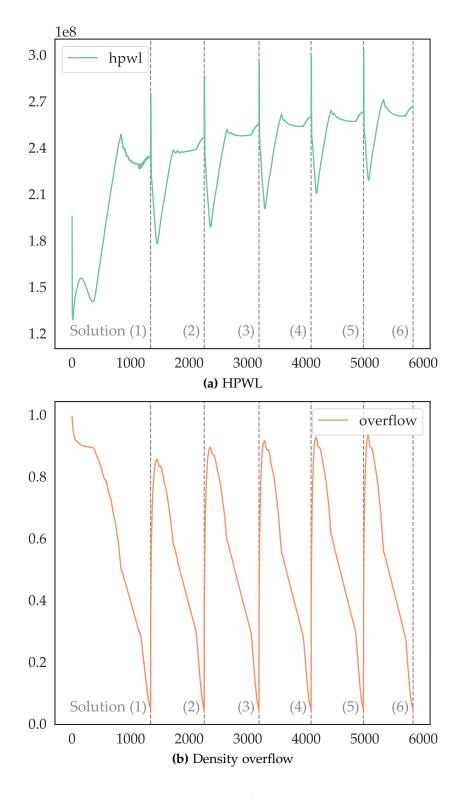

| 4.5 | HPWL and density overflow curves for superblue12                                             | 49 |

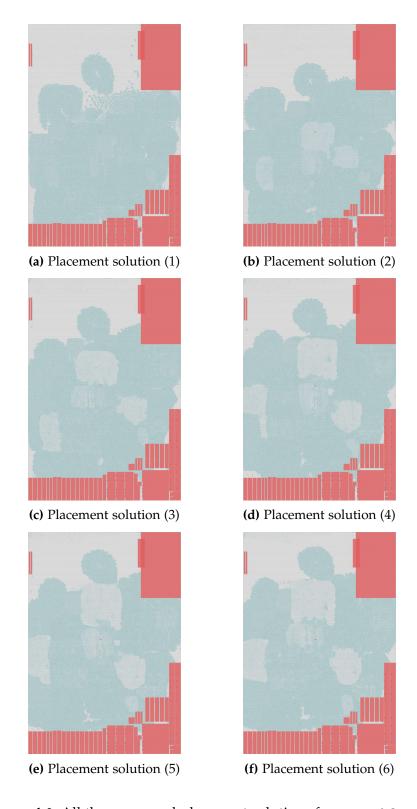

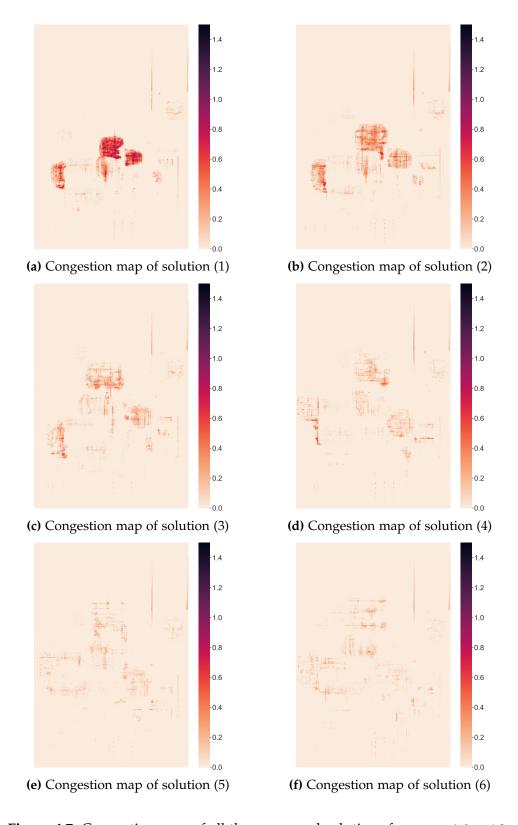

| 4.6 | All the converged placement solutions for superblue12                                        | 50 |

| 4.7 | Congestion map of all the converged solutions for superblue12                                | 51 |

| 4.8 | Runtime breakdown of Xplace-Route on ISPD 2015 benchmarks                                    | 56 |

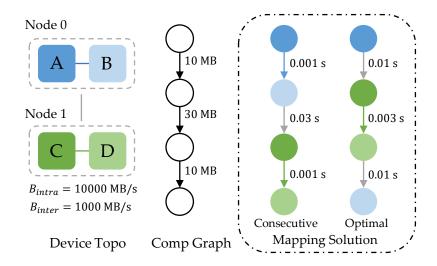

| 5.1 | An example to show consecutive mapping cannot guarantee optimality                           | 59 |

| 5.2 | The workflow of optimizing the pipelined training throughput of using                        |    |

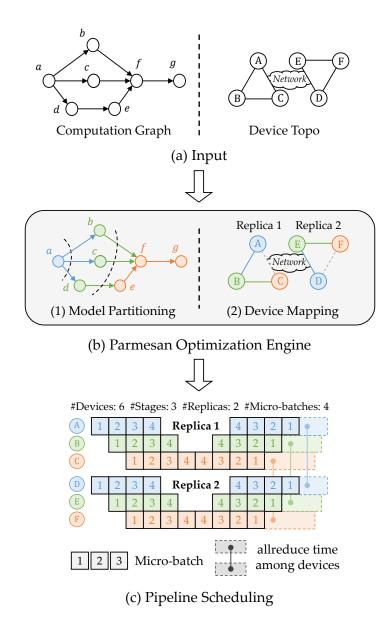

|     | Parmesan                                                                                     | 61 |

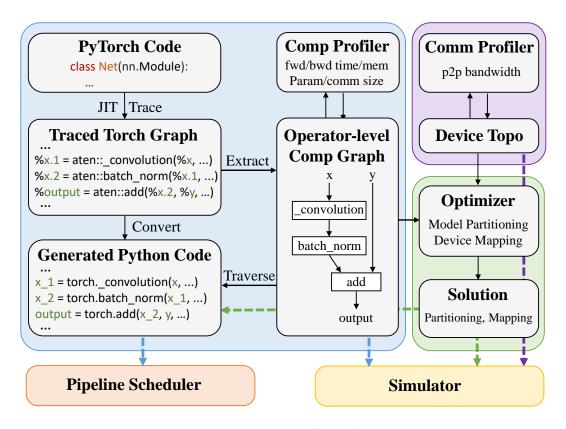

| 5.3 | The whole workflow of Parmesan                                                               | 76 |

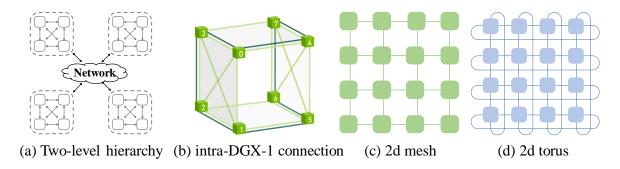

| 5.4 | Visualization of different device topologies                                                 | 78 |

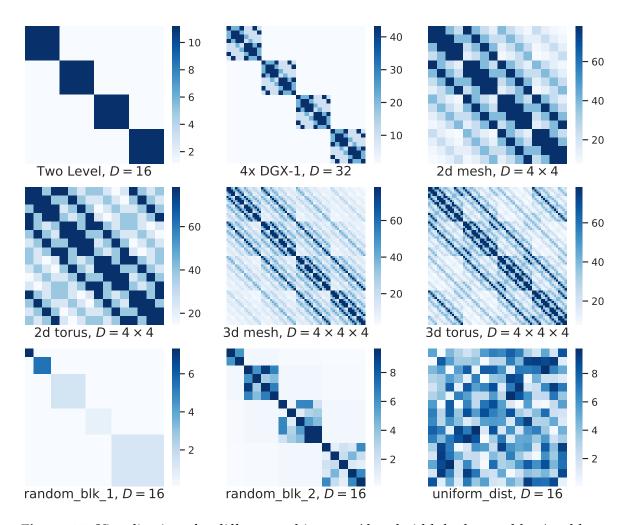

| 5.5 | Visualizations for different architectures' bandwidth look-up-tables                         | 80 |

| 5.6 | Throughput of different BERTs and Swins on 4x DGX-1 Architecture                             | 85 |

| 5.7 | Effectiveness of operator clustering                                                         | 88 |

| 5.8 | A visualization of different mapping algorithms on a two-level hierarchical                  |    |

|     | architecture for Pipedream's Swin-L (8,2) partitioned results                                | 92 |

| 5.9 | A comparison between the simulated and real-world throughput                                 | 94 |

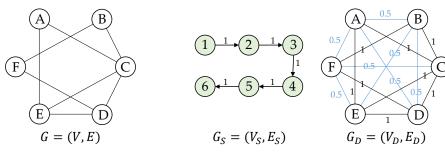

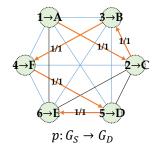

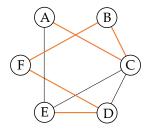

5.10 The Hamiltonian path problem on G can be reduced to the device mapping problem between the stage graph  $G_S$  and the device topology graph  $G_D$ . . . 97

## **List of Tables**

| 3.1  | Benchmarks Statistics                                                            | 34 |

|------|----------------------------------------------------------------------------------|----|

| 3.2  | HPWL and runtime results on ISPD 2005 contest benchmarks                         | 35 |

| 3.3  | HPWL, Top5 overflow, and runtime results on ISPD 2015 contest benchmarks         | 36 |

| 3.4  | Ablation studies of the operator-level optimization techniques                   | 38 |

| 4.1  | DR metrics and runtime results on ISPD 2015 contest benchmarks                   | 54 |

| 4.2  | Ablation studies of proposed routability optimization techniques                 | 56 |

| 5.1  | Synthesised bandwidths mesh/torus architecture                                   | 79 |

| 5.2  | DNN Models used in two-level hierarchical and non-regular architectures          | 81 |

| 5.3  | DNN Models used in cloud 4x DGX-1 architecture                                   | 81 |

| 5.4  | A comparison with relevant baselines on the two-level hierarchical architecture. | 82 |

| 5.5  | A comparison with Pipedream on 4x DGX-1                                          | 86 |

| 5.6  | Simulation results for different topologies                                      | 86 |

| 5.7  | The relative speedup of our refinement technique                                 | 87 |

| 5.8  | Runtime of device mapping with different $(S, R)$ and device topologies          | 90 |

| 5.9  | Comparison on results quality of device mapping with timeout heuristic to        |    |

|      | that of the optimal version                                                      | 91 |

| 5.10 | The cases that our mapping algorithm maps the model partitioning in a            |    |

|      | non-regular manner                                                               | 92 |

| 5.11 | Simulation results for different topologies                                      | 93 |

# Chapter 1

# Introduction

## 1.1 Graphics Processing Unit

The *graphics processing unit* (GPU) has a rich history. Originally conceived to enable the visualization of images and the simulation of real-world scenarios within virtual environments, GPUs have undergone remarkable advancements over the decades. This growth is depicted in Figure 1.1, showing the exponential increase in transistor count. As a result, the continuous evolution of GPUs has yielded numerous benefits, including enhanced gaming experiences, expanded range of desktop applications, and significant contributions to the progress of various industries. Today, GPUs have transformed into an essential component of the digital world, occupying an ever more vital role in modern life.

As computing power continues to advance, GPUs have emerged with a superior performance compared to central processing units (CPUs) in certain specialized computing domains. Modern GPUs are characterized by high parallelism, making them particularly well-suited for computationally intensive tasks, especially those that can be effectively divided into multiple independent subtasks. In scientific computing with tasks involving vector operations, matrix multiplication and fast Fourier transform, GPUs exhibit significantly faster computation speeds compared to CPUs. Besides the continuous improvement in computing power, the GPU software ecosystem has also flourished spontaneously. A wide

Figure 1.1: Transistor count on NVIDIA and AMD (ATI) GPUs. Data from Wikipedia [123].

range of GPU programming languages and libraries [117, 100, 104, 1] have been developed, offering optimized implementations of GPU-friendly algorithms and effectively leveraging the potential of GPUs.

The continuous advancement of computing power and software ecosystems has facilitated the widespread adoption of GPUs across diverse fields. In addition to their traditional applications in graphics and gaming, modern GPUs have found utility in scientific computing, cryptocurrency, artificial intelligence (AI), and electronic design automation (EDA), among others. In artificial intelligence, a significant advancement of GPU was made by [106], which pioneered the adoption of GPU acceleration in deep learning. This pioneering effort resulted in a remarkable increase in the speed of training deep neural networks (DNNs). Subsequently, utilizing GPUs for DNN training acceleration became increasingly prevalent, greatly propelling the progress of AI [37, 21, 27]. With the expansion of data sizes and the increasing complexity of models, a growing number of researchers have turned their

attention to optimizing machine learning systems (MLSys) for training large-scale DNNs, leading to the development of various algorithms that are specifically designed to address the challenges associated with multi-GPU training [107, 113, 51, 136]. Within the EDA domain, GPUs have also played a crucial role. Recently, GPU acceleration was introduced to tackle the very large-scale integration (VLSI) placement problem with impressive success in terms of runtime speedup [19, 80]. Besides this achievement, GPU acceleration quickly gained widespread adoption and found extensive application in other critical EDA problems. These problems encompass areas such as logic synthesis [75], placement [29, 34], timing analysis [33, 30, 31], routing [32, 77, 76] and design rule checking [41], where GPU acceleration shows high effectiveness and efficiency.

#### 1.2 Placement Problem

Placement is a critical yet challenging combinatorial optimization problem. Its core objective is to effectively place various components within a given space, optimizing specific objectives while satisfying predefined constraints. Because of its direct correlation to solution quality, placement has been extensively studied in various research domains, including but not limited to VLSI placement in EDA and device placement in MLSys. Figure 1.2 illustrates these two critical placement problems.

#### 1.2.1 VLSI Placement in EDA

The rapid growth in the number of transistors in VLSI design has led to a continuous increase in the computing power of modern chips. VLSI circuit, being integral to various aspects of life, such as mobile phones, personal computers, cars and more, significantly enhances the quality of modern living. However, the process of designing VLSI circuits is extremely complicated. Within the design flow, electronic design automation (EDA) stands out as one of the most challenging parts, which involves register-transfer level generation, logic synthesis, placement, routing and verification [54]. These intricate steps are vital for ensuring successful fabrication and manufacturing of VLSI circuits.

**Figure 1.2:** Illustration for VLSI placement and device placement.

Among the above steps in EDA flow, *VLSI Placement* holds an essential and foundational role due to the strong correlation between the placement solution quality and the circuit's PPA (power, performance and area). Meanwhile, modern circuits contain millions of standard cells, which highly increases the computational complexity of the placement problem and brings huge challenges to the leading-edge global placers.

To address the aforementioned challenge, VLSI placement is commonly decoupled into two consecutive phases: global placement and detailed placement. During the global placement (GP) phase, the primary goal is to minimize the interconnect wirelength between standard cells while guaranteeing an even distribution of cells. In addition, various objectives such as timing [34], routability [17] and power [74] are considered to further optimize the circuit's PPA. In the detailed placement (DP) phase, a global-placed solution is first legalized, satisfying the non-overlapping constraints while minimizing cell displacement. The DP phase then further optimizes the placement objectives with the solution legality maintained.

#### 1.2.2 Device placement in MLSys

In recent years, the importance of machine learning systems (MLSys) has grown continuously, driven by the remarkable success of DNNs in artificial intelligence. The ever-increasing

DNN model size [37, 21, 85, 27] significantly stimulates the development of distributive learning scheme in pursuit of more efficient large-scale DNN training [51, 107, 7]. In response to such escalating demands, both researchers and industrial practitioners have been actively exploring dedicated model parallel schemes, with the objectives of improving (1) model throughput over the given device instances; (2) flow effectiveness in terms of network and device topology coverage; and (3) turnaround efficacy for searching a desirable parallelism strategy.

However, designing high-performance distribution strategies for different neural network architectures over different device topologies is non-trivial and challenging, because of the astronomically large search space brought by the growing model size and complex device interconnects. Various paradigms, including but not limited to data parallelism [26, 63, 139], model parallelism [18, 50, 113] and pipeline parallelism [49, 67, 68, 97, 23, 96], have been extensively studied to enable decent parallel execution.

As one of the most prevailing techniques, pipeline parallelism mainly covers two types of optimization problems, pipeline scheduling and device placement. Pipeline Scheduling schedules the pipelined stages for computation and communication considering other scheduling factors like pipeline flush, weight buffering and update mechanisms, etc., with the objective of finding the best tradeoff among device-utilization, memory footprint and training convergence (for asynchronous training).

Orthogonal to pipeline scheduling, device placement places thousands or even millions of DNN operators on a large-scale distributed system to maximize the training throughput with consideration of the interconnected bandwidth and peak memory constraint. Due to the extremely high computational complexity, device placement for a multi-GPU system is usually decoupled into two consecutive stages: (1) Model Partitioning: model parameters and associated activations are partitioned into a set of stages, where the workload of each stage is deployed on an individual device. This step aims to balance the workloads among all stages as well as to maximize the overall throughput. (2) Device Mapping: partitioned stages are physically placed on the devices with consideration of the hardware constraints,

network topology and communication bandwidths. This step affects network traffic and computing resource utilization which turns out to be crucial for large-scale DNN training.

#### 1.3 Overview of this Thesis

In this thesis, we study and investigate two important problems relating to placement and GPU: GPU-accelerated VLSI placement in EDA and device placement for GPUs in MLSys.

Chapter 2 conducts a literature review on the placement problem, including VLSI placement and device placement.

For GPU-accelerated VLSI placement, we first propose an extremely fast and extensible VLSI placement framework with GPU acceleration in Chapter 3. We also integrate a novel Fourier neural network into the proposed framework as an extension to enhance the solution quality. Chapter 4 further enables our framework to handle the detailed-routability-driven VLSI placement problem by effective GPU parallelization schemes and routability optimization techniques.

Regarding device placement for GPUs, Chapter 5 introduces an efficient design framework that effectively addresses the problem. We demonstrate the effectiveness of our proposed approach in maximizing DNN training throughput on a general device topology. Furthermore, we explore the potential for migrating the algorithm to a system with heterogeneous interconnection.

In summary, this thesis explores the potential of GPU in placement and proposes a set of algorithms to address two fundamental yet challenging combinatorial problems when placement meets GPU.

# Chapter 2

# Literature Review

In this chapter, we will review the literature on placement-related problems, including VLSI placement in EDA and device placement in MLSys.

#### 2.1 VLSI Placement in EDA

VLSI Placement plays a crucial role in the EDA flow, as it has a significant impact on the overall quality of the circuit's PPA. Modern VLSI placers commonly employ analytical models to optimize the placement solution with consideration of various objectives such as wirelength, density and routability. Due to the extremely high computational complexity of the placement problem, GPU acceleration for VLSI placement has achieved notable success by leveraging the power of GPUs.

In Section 2.1.1, we will look into various analytical placers. In Section 2.1.2, we will review routability optimization techniques for placement. In Section 2.1.3. we will study recent advancement in GPU-accelerated placement.

#### 2.1.1 VLSI Placement

The VLSI placement problem is a classical problem and has been vigorously studied. Various methods, such as cluster-growth [111], simulated annealing [112, 119, 94] and min-cut [5,

109, 120], have been proposed to tackle it. With the growing computational complexity of the placement problem, analytical approach has emerged as a widely adopted solution today. Over the past few decades, various kinds of CPU-based analytical placers have been introduced. These analytical placers aim to optimize the half-perimeter wirelength (HPWL) of the placement, which is essential for achieving efficient VLSI circuits. Based on their formulations of the objectives and constraints, these placers can be broadly classified into two types: quadratic placers and non-linear placers.

Quadratic VLSI Placement: Quadratic placers like GORDIAN [62] employed clique expansion to represent a net (a hypergraph), formulated the placement as a quadratic programming (QP) problem, and solved it using the well-known conjugate gradient method [42]. Eisenmann et al. [22] introduced the concept of cell spreading force, which was computed using Poisson's equation. FAR [47] inserted fixed points in the placement region to guide cells towards low-density areas. FDP [56] implemented a dynamic force weight to accelerate convergence.

To reduce the high computational complexity brought by the clique model, Fast-Place [124] proposed a hybrid net model that combines clique models for two-pin and three-pin nets with star models for high-pin nets. This hybrid model effectively reduces the number of non-zero elements in the cell adjacency matrix, resulting in faster solving time. To evenly distribute cells and balance their distribution, FastPlace adopted cell shifting and introduced pseudo nets to connect on-boundary pseudo pins with real cells. Building upon FastPlace, RQL [125] supported on-die pseudo pins, offering greater flexibility. To provide a better approximation of half-perimeter wirelength (HPWL), Kraftwerk2 [116] studied the limitation of the clique-based net model and proposed Bound2Bound (B2B) net model, which considers only the boundary pins in the quadratic cost. For cell overlap control, Kraftwerk2 modeled cell density by an area supply and cell demand system, formulating it as Poisson's equation to achieve uniform cell distribution. Besides Poisson's equation-based method, DPlace [91] proposed a diffusion-based placement framework aimed at effectively distributing cells in a smooth manner.

SimPL [58, 60] developed an iterative lower-upper-bound strategy, with the lower-bound round solving the quadratic wirelength problem with pseudo-net-based spreading force and the upper-bound round incorporating look-ahead rough legalization (LAL) to address cell overlap while maintaining relative cell positions. The legalized positions serve as anchors in the next iteration, guiding the optimization process. ComPLx [59] generalized SimPL by primal-dual Lagrange relaxation and provided convergence analysis. Based on the lower-upper-bound framework, POLAR [78, 79] proposed an efficient rough legalization method based on region expansion and investigated the possibility of developing an effective CPU-parallel quadratic placer.

*Non-Linear VLSI Placement:* Although quadratic placers can converge quickly, their solution qualities are limited by the low modeling order of the wirelength. Non-linear placers approximate wirelength by a smooth version of the HPWL metric and relax the cell density constraint as a penalty term. Different from quadratic placers, non-linear placers produce higher solution quality while the running time overhead is huge.

The log-sum-exp (LSE) function is widely used as a non-linear approximation for the HPWL. The placer mPL6 [12, 13] employed the LSE function as its wirelength model and formulated the density control problem by a Helmholtz equation. The resulting unconstrained problem is solved by the explicit Euler method. Besides, mPL6 incorporated the multi-level optimization technique to tackle the scalability challenges. APlace [52, 53] utilized a differentiable bell-shaped function to model cell density and formulated a quadratic penalty term for this density function. The problem is then solved by the conjugate gradient (CG) method, which incorporates a line search. Similar to APlace, NTUplace3 [16] also applied a bell-shaped function to model cell density and solved the problem by CG. However, NTUplace3 incorporated the CG method with a dynamic step-size control for runtime speedup and introduced Gaussian smoothing for large macro. Furthermore, NTUplace3 proposed white-space allocation to address cell density overflow.

Compared to the LSE model, the weighted-average (WA) wirelength model [45, 44] offers several advantages. In theory, the WA model has a smaller estimation error of HPWL,

and empirical studies have shown better solution quality. As a result, the WA wirelength model has gained considerable prominence in recent years.

Lu et al. [88, 89, 90] introduced a novel approach called ePlace, which utilizes an electrostatics-based method to solve the placement problem. This method had shown significant improvements in quality compared to previous analytical placers. Concretely, ePlace incorporated the WA wirelength cost and models the cell density problem as an electrostatic system (formulated as Poisson's equation). In this electrostatic model, cells are treated as charges and are evenly distributed using electric force. To effectively solve the whole non-linear problem, ePlace applied the Nesterov's method [99] and employed dynamic steplength. Additionally, ePlace utilized discrete cosine [6, 114] transformation to accelerate density computation. Building upon ePlace, Pplace [137] extended the computation of electric potential to an infinite series, providing a convergence proof. Another closely related placer, RePlAce [17] dynamically adjusted the density penalty function based on historical information, resulting in a further boost to the solution quality.

Besides the WA wirelength and electrostatics-based methods, recent research has explored various techniques to further enhance the quality of non-linear placers. GAML [138] utilized the augmented Lagrangian method to tackle the non-linear global placement problem, accompanied by a theoretical convergence guarantee. BiG [118] investigated the feasibility of a bivariate wirelength model, which has low approximation error and high numerical stability. The work [15] proposed a parameter-free quadratic-programming-based initialization method. This method focused on generating better initialization for non-linear placement, leading to improved optimization results and overall solution quality compared with using random initialization.

Machine-learning-based approaches have also emerged as valuable techniques in assisting the VLSI placement step. Mirhoseini et al. [92] developed a method based on graph neural network (GNN) for the macro placement problem and adopted reinforcement learning to optimize the circuit's PPA. The work [3] introduced reinforcement learning for parameter tuning in the placement process. PL-GNN [87] employed GNN to cluster

cells and to guide the optimization of a commercial placer. AutoDMP [4] utilized Pareto optimization to explore the placement parameter space.

#### 2.1.2 Routability Optimization in VLSI Placement

Besides the commonly used metric of HPWL, routability is another crucial metric to measure the quality of a placement solution. Effectively estimating and reducing routing congestion are key challenges in routability-driven placement.

Congestion estimation methods can be broadly categorized into probabilistic-based, machine-learning-based and router-based approaches. Probabilistic-based methods [86, 129, 9, 46, 39, 115] decompose multi-pin nets into two-pin nets and enumerate all possible detour-free routing solutions. By computing a probabilistic routing usage map, the placement congestion optimization can be guided. Machine-learning-based methods [130, 134, 83, 25, 14] prevail recently. They utilize deep neural networks to predict the routing congestion map and guide routability optimization. Compared to probabilistic-based and machine-learning-based methods, router-based methods provide higher congestion estimation accuracy and better solution quality. They invoke an internal or external global router to produce a real routing solution, offering valuable congestion information for the placers. Due to its high accuracy, router-based methods are widely applied in routability-driven placers to estimate routing congestion [102, 57, 38, 20, 48, 17].

To reduce routing congestion, there are different techniques including white-space allocation, local density adjustment, cell swapping and cell inflation. The works [133, 65] allocated white space to congested areas so that routing congestion can be alleviated. APlace [53] and NTUplace4h [46] adjusted the local density penalty to push cells away from congested areas. IPR [102] and RippleDP [66] applied cell swapping for congestion removal in the detailed placement stage while CROP [135] and Starfish [127] adopted this technique in the post-placement stage. Cell inflation [43] is a technique that inflates cells in congested areas using historical information, aiming to address the pin-accessibility problem. Due to its simplicity and effectiveness, this technique is widely adopted in routability-driven

placers to reduce routing congestion [39, 57, 38, 20, 17, 48, 73, 72].

Modern routability-driven placers such as SimPLR [57], Ripple 2.0 [38], Eh?Place [20], NTUplace4dr [48] and RePlAce [17], invoked router-based congestion estimation methods and incorporated multiple congestion removal techniques mentioned above to effectively enhance routability. These placers demonstrated their effectiveness in achieving a cooptimization between HPWL and routability. It is worth noting that SimPLR, Ripple 2.0 and RePlAce only verified their solution with an academic global router NCTUgr [84] and lacked a detailed-routability evaluation. Eh?Place and NTUplace4dr handled detailed-routability by customized schemes that invoke a computationally intensive global router during global placement, largely affecting its runtime efficiency.

#### 2.1.3 GPU-Accelerated VLSI Placement

With the rapid development of GPU's computational power, GPU acceleration becomes an important direction to pursue to handle large-scale problems with parallelism. In global placement, the work [19] accelerated multi-level analytical placer mPL6[12] with GPU by parallelizing the computation of the wirelength function and the spreading force, achieving around 15× speedup. The work [71] explored the idea of utilizing sparse matrix multiplications to compute wirelength and adopting a flattening technique for area computation. However, the maximum wirelength degradation in [19] is larger than 5% and the work [71] does not report their solution quality in details.

Recently, DREAMPlace [80] implemented the approach of ePlace [90] on GPU by casting the placement problem as a neural network training problem and demonstrated the superiority of GPU-accelerated global placers. DREAMPlace conducted a study on GPU-accelerated wirelength and density operators, employing various parallelization algorithms. In terms of wirelength computation acceleration, DREAMPlace explored both pin-level and net-level parallelization techniques and observed that net-level parallelization yielded a higher speedup. To parallelize the cell density operator, DREAMPlace employed multi-threading to compute the density contribution of each cell. Additionally, DREAMPlace utilized the

fast Fourier transform (FFT) provided by PyTorch [104] to compute the electrostatics-based density force. In comparison to RePlAce [17], DREAMPlace not only produced more than 40x runtime speedup on average for large benchmarks but also provided an open-source analytical placement framework for researchers to further develop. As for routability optimizatin, DREAMPlace integrated NCTUgr for routability evaluation and employed cell inflation to mitigate routing congestion. Although DREAMPlace achieves the state-of-the-art solution quality and performance, it primarily focused on accelerating the wirelength and density operators on GPU while lacking a more general operator-level optimization.

Expanding upon DREAMPlace, the work [35] proposed an effective density accumulation method using parallel partial summation. Gu et al. [29] introduced a multi-electrostatics system to tackle the fence region constraint and implemented a quadratic density penalty to accelerate convergence. Liao et al. [70] developed a net weighting technique that employed a momentum method to tackle the timing-driven placement problem. Guo et al. [34] derived the gradient of the Elmore delay model and integrated it into the placement stage to make the timing-driven global placement objective differentiable. Yang et al. [132] explored the acceleration of the legalization step on CPU/GPU heterogeneous platforms through task scheduling. Additionally, ABCDPlace [81] conducted an investigation to boost the runtime efficiency of detailed placement by leveraging GPU parallelization. It explored batch-level parallelism for traditional sequential detailed placement operators such as independent set matching, global swapping and local reordering, achieving around 10x speedup through GPU acceleration. In the case of independent set matching, ABCDPlace split cells into smaller subsets and concurrently solved the matching problem for each subset. For global swapping, ABCDPlace parallelized the candidate collection and cost calculation, which led to faster runtimes. In terms of local reordering, ABCDPlace introduced parallel sliding windows to decompose the reordering problem into independent sub-problems and solved them in parallel.

## 2.2 Device Placement in MLSys

The impressive achievements of DNNs have led to a significant increase in the importance of machine learning systems (MLSys) over the past few years. In MLSys, DNN training parallelism has emerged as an important research direction, as it plays a critical role in optimizing training efficiency. Recently, various parallelism strategies and optimization techniques are proposed to achieve effective parallelization.

In Section 2.2.1, we will begin by reviewing two classical parallelism schemes, namely data parallelism and model parallelism. In Section 2.2.2, we will study the widely adopted pipeline parallelism. In Section 2.2.3, we will review the device placement problem.

#### 2.2.1 Data and Model Parallelism

Data parallelism partitions training data at the batch level and enables model training to scale up to a distributed system [26, 63, 139]. Each device maintains a *replica* of the entire model and computes gradient synchronously by a technique called *allreduce* [105]. The computed gradient is then applied to update the model parameters. However, for a large model, pure data parallelism is infeasible because of the insufficient device memory to support model training or the large communication overhead caused by gradient synchronization.

Model parallelism is an alternative option to address the issue that the memory of a device is insufficient to maintain a DNN. By partitioning the DNN into multiple disjoint sets and distributing them across different devices, model parallelism enables the training of large models. However, traditional model parallelism approaches, as discussed in [18], suffered from limited resource utilization as they activate only one device at a time. Megatron-LM [113] explored tensor-level model parallelism to partition Transformer-based models to boost computational efficiency while requiring heavy-load collective communication for synchronization. FlexFlow [50] integrated tensor-level model parallelism with data parallelism and randomly searched the parallelization strategies according to the simulated throughput.

**Figure 2.1:** An example of GPipe's fashion pipeline parallelism with four partitioned stages and four micro-batches.

#### 2.2.2 Pipeline Parallelism

Pipeline Parallelism aims at scheduling DNN training more elaborately to boost resource utilization. Extending from model parallelism, pipeline parallelism not only partitions a DNN to different devices but also divides a mini-batch of training data into several micro-batches. In pipeline parallelism, the split micro-batches and the partitioned DNN will be delicately scheduled, resulting in an increase in throughput.

One notable technique is GPipe [49] as shown in Figure 2.1. GPipe split the minibatch into micro-batches and performs synchronous scheduling of forward and backward propagation during training. Although GPipe effectively increases training throughput, it requires additional device memory. DAPPLE [23] introduced a hybrid parallelism strategy (i.e., pipeline training combined with data parallelism) with an one-forwardone-backward (1F1B) synchronous pipeline. This technique reduces the peak memory consumption compared to the GPipe scheme. HetPipe [103] extended support for the hybrid parallelism strategy on heterogeneous GPU clusters. PipeDream [96] generalized the pipeline training in an asynchronous fashion and reduces the idling time (bubble). However, the asynchronous pipeline requires maintaining stale versions of weights for backward propagation, which can lead to accuracy degradation. PipeDream-2BW [97] proposed a double-buffered update technique to reduce the number of weight versions and save device memory usage. PipeMare [131] mitigated the accuracy loss through learning rate rescheduling and weight discrepancy correction. Chimera [67] further extended the synchronous pipeline to a bidirectional pipeline and achieves impressive throughput. TeraPipe [68] explored token-level pipeline parallelism specifically designed for Transformerbased language models and investigated a dynamic programming-based algorithm to search for the optimal execution flow. Additionally, the work in [98] extended Megatron-LM to support pipeline parallelism and introduced an interleaved 1F1B pipeline to boost utilization. Despite of the significant improvements in training efficiency achieved by these pipeline schedulers, they still lack a robust and effective device placement algorithm to achieve good DNN training throughput on general device topology.

#### 2.2.3 Device Placement for GPUs

Orthogonal to pipeline scheduling, device placement is another important factor to maximize the training throughput. Its goal is to optimize the placement of DNN operators on a distributed GPU system. With modern DNNs consisting of millions of operators and distributed systems having diverse interconnected bandwidths, the problem complexity significantly increases.

One approach to solving this problem is the application of machine learning-based methods. The works [93, 24, 101] employed reinforcement learning to place DNNs on GPUs, using the resulting throughput as a training reward. However, these machine-learning-based methods often require time-consuming online throughput measurements, which can largely impact the overall runtime.

To tackle the growing problem complexity and achieve efficient yet practical device placement, recent advanced device placement approaches are usually divided into two consecutive stages: model partitioning and device mapping. These two-stage methods balance DNN partitions and properly map the partitions to devices.

**Model Partitioning** For model partitioning, PipeDream [96] employed a dynamic programming based (DP-based) method. The primary objective of the dynamic programming algorithm employed by PipeDream is to minimize the maximum stage time, aiming to achieve effective pipeline scheduling and maximize device utilization. This algorithm considers computation and communication time to balance the stage times. Due to its

effectiveness, this DP-based approach has gained popularity. DAPPLE [23] extended the dynamic programming to consider the warmup and allreduce operations in pipeline training. Piper [122] supported a wider range of connection types in the computational graphs.

However, PipeDream, DAPPLE and Piper primarily focused on coarse-grained layer-level granularity, limiting their flexibility. In contrast, RaNNC [121] proposed a three-phase flow for operator-level graph partitioning. In the first phase, RaNNC atomically merges operators that are not descendants of the model input to reduce the size of the operator-level graph. In the second phase, computation blocks are constructed through k-way multi-level partitioning to balance the computation and communication costs. Finally, in the third phase, partitions are formed using dynamic programming, considering computation time, communication cost and memory usage. Alpa [136] further considered intra-operator parallelism through an integer linear programming approach. Different from RaNNC, Alpa clustered atomic operators using dynamic programming with consideration of the operator computation cost and connectivity. However, the model partitioning methods employed by both RaNNC and Alpa only focused on a specific topological order of a DNN, which may affect adversely the partitioning quality.

**Device Mapping** As for device mapping, RaNNC [121] assumed a flattened device topology of constant bandwidth, neglecting more complex topologies. However, the flattened topology is not practical in the real world since it is difficult to maintain constant bandwidth in a large-scale GPU cluster.

Instead of assuming constant bandwidth, DAPPLE [23] explored the compositions of three predefined policies (fresh, append and scatter) to generate final placement on a system with hierarchical interconnection while lacking a guarantee of solution quality. PipeDream [96] and Piper [122] addressed the hierarchical topology mapping problem by leveraging dynamic programming, where the planning at level L considers placement on  $K_L$  "superdevices" (each contains  $K_{L-1}$  "superdevices" from level L-1) according to the topology at level L. Alpa [136] generalized the dynamic programming algorithm to further consider all possible device combinations in hierarchical architectures. For example, given 2

nodes and 4 GPUs per node, Alpa considered them as  $2 \times 4$ ,  $1 \times 8$ ,  $4 \times 2$  or  $8 \times 1$ . While PipeDream, Piper and Alpa integrated partitioning and mapping into a unified dynamic programming algorithm, they only tackled the hierarchical topology mapping problem and did not provide a general mapping algorithm for arbitrary device topologies.

# Chapter 3

# **GPU-Accelerated VLSI Placement**

In this chapter, we develop Xplace, an efficient yet extensible GPU-accelerated placement framework built on top of PyTorch [104], to consider factors at operator-level optimization. Xplace not only achieves better performance and quality than DREAMPlace but also shows high extensibility to incorporate neural network into analytical placer. The source code of Xplace is released on GitHub<sup>1</sup>. Our key contributions are summarized as follows.

- Efficiency: with operator combination, operator extraction, operator reduction and operator skipping, Xplace achieves around 3x speedup per GP iteration compared to the state-of-the-art global placer DREAMPlace. A placement-stage-aware parameter scheduling technique is also proposed to improve the solution quality. Experimental results show that Xplace achieves around 2x speedup with better solution quality compared to DREAMPlace.

- Extensibility: we plug into Xplace a novel Fourier neural network as an extension. The neural network serves as a global guidance for placement. Experimental results not only show that the proposed framework can further improve the solution quality but also illustrates the possibility of adopting neural guidance in analytical global placement.

<sup>1</sup>https://github.com/cuhk-eda/Xplace

## 3.1 Preliminaries

Given a placement circuit G = (V, E), V represents the set of cells and E denotes the set of nets. Let  $p = \{(x_1, y_1), ..., (x_N, y_N)\} \in \mathbb{R}^{N \times 2}$  denote the 2D positions of the cells, where N is the number of cells. The placement region R is uniformly split into an  $M_r \times M_c$  grid R. The objective of placement is to minimize the total HPWL of all the nets while satisfying the cell density constraint, which is formulated as,

$$\min_{p} HPWL(p) = \min_{p} \sum_{e \in E} HPWL_{e}(p)$$

(3.1a)

s.t.

$$D_b \le D_t, \forall b \in B$$

(3.1b)

where  $D_b$  and  $D_t$  denote bin b's cell density and the benchmark-given target density respectively. The HPWL of net e is defined as follows:

$$HPWL_e(p) = (\max_{i \in e} x_i - \min_{i \in e} x_i) + (\max_{i \in e} y_i - \min_{i \in e} y_i). \tag{3.2}$$

Because the HPWL in Equation (3.2) is not differentiable, analytical placement reformulates the objective with a smooth approximation of HPWL equipped with a cell density penalty to relax the cell density constraint:

$$\min_{p} \sum_{e \in E} WL_{e}(p) + \lambda D(p)$$

(3.3)

where the wirelength  $WL_e(p) = WL_e(x) + WL_e(y)$  is modeled as the weighted-average (WA) [45] wirelength with a coefficient  $\gamma$ ,

$$WL_{e}(x) = \frac{\sum_{i \in e} x_{i} e^{x_{i}/\gamma}}{\sum_{i \in e} e^{x_{i}/\gamma}} - \frac{\sum_{i \in e} x_{i} e^{-x_{i}/\gamma}}{\sum_{i \in e} e^{-x_{i}/\gamma}}$$

(3.4)

and similarly for  $WL_e(y)$ . A smaller  $\gamma$  leads to more accurate approximation of HPWL. The parameter  $\lambda$  (Lagrange multiplier) controls the weight of the cell density penalty D(p). A typical placement flow starts with a small  $\lambda$  and gradually increase it to remove cell overlaps.

In ePlace [90] on which Xplace is based, each cell *i* is modeled as a charge, and the cell density is modeled as an electrostatic system denoted as:

$$\begin{cases}

\nabla \cdot \nabla \psi(x, y) = -\rho(x, y), \\

\hat{\mathbf{n}} \cdot \nabla \psi(x, y) = \mathbf{0}, (x, y) \in \partial R, \\

\iint_{R} \rho(x, y) = \iint_{R} \psi(x, y) = 0,

\end{cases} (3.5)$$

where  $\partial R$  is the boundary of the placement region,  $\rho(x,y)$  is the electron density map,  $\psi(x,y)$  is the electric potential distribution, and  $\xi(x,y) = -\nabla \psi(x,y)$  is the electric field distribution. The numerical solution of Poisson's equation in Equation (3.5) is derived by discrete cosine transformation (DCT) in [90].

## 3.2 Overview of Xplace

In this section, we will discuss the design of Xplace, a fast and extensible GPU-accelerated placer. Our Xplace framework is shown in Figure 3.1. Xplace is built on top of PyTorch and contains a placement core engine. Inside the core engine, the gradient engine takes cell position and placement parameters as input to compute the cell gradient. Next, the optimizer utilizes the computed gradient to update the cell position. The evaluator evaluates the placement solution, and the recorder records the placement metrics like HPWL and overflow. Finally, the scheduler decides how to modify the parameters and whether to stop the global placement. It is worth noting that all these parts are designed as independent modules in Xplace so that one can easily extend Xplace by applying new scheduling techniques, new gradient functions, new placement metrics and so on.

Section 3.3 will discuss several important technical details that enable Xplace running very efficiently on GPU. We propose operator-level optimization techniques to achieve effective parallelization. Section 3.4 will discuss a placement-stage-aware parameters scheduling to improve the solution quality. Section 3.5 will extend Xplace with a Fourier neural operator to show its high extensibility.

**Figure 3.1:** Overview of Xplace

## 3.3 Operator-Level Optimization

#### 3.3.1 Wirelength Operator Combination

Weighted average (WA) [45] wirelength is used as the wirelength objective in many analytical global placers. In Xplace, we adopt the WA wirelength in Equation (3.4) as our wirelength objective and update the cell position based on the guidance of the WA gradient. To avoid numerical overflow, a numerically stable version of the WA wirelength is given in Equation (3.6) which needs the minimum and the maximum position among all pins in a net.

$$WL_{e}(x) = \frac{\sum_{i \in e} x_{i} e^{\frac{x_{i} - \max_{j \in e} x_{j}}{\gamma}}}{\sum_{i \in e} e^{\frac{x_{i} - \max_{j \in e} x_{j}}{\gamma}}} - \frac{\sum_{i \in e} x_{i} e^{\frac{\min_{j \in e} x_{j} - x_{i}}{\gamma}}}{\sum_{i \in e} e^{\frac{\min_{j \in e} x_{j} - x_{i}}{\gamma}}}$$

(3.6)

A wirelength objective-and-gradient merging method, proposed in [80], computes both the WA wirelength and the WA gradient within a single GPU thread to mitigate memory bounded problems.

Since both the HPWL function in Equation (3.2) and the stable WA wirelength function in Equation (3.6) need the minimum and maximum cell positions in a net, we further modify this merging method by combining the three operators with heavy wirelength-related workload, WA wirelength, WA gradient and HPWL, into one operator to avoid redundant computation of the minimum and maximum function. The proposed operator combination technique can significantly reduce the total GPU execution time.

#### 3.3.2 Density Operator Extraction

Density objective is one of the most computationally intensive operators in global placement. Similar to [80] and [71], we implemented a GPU-accelerated area accumulation operator to compute the cell density map and apply PyTorch built-in rfft2/irfft2 operators to derive the numerical gradient of the electrostatic system in Equation (3.5). We also implemented a GPU-accelerated version of the overflow ratio operator *OVFL*, whose CPU version is applied in NTUplace3 [16] and ePlace [88], to measure the evenness of cell distribution and guide the parameter update. The overflow ratio is described as,

$$OVFL = \frac{\sum_{b \in B} \max(D_b - D_t, 0) A_b}{\sum_{i \in V_{mon}} A_i}$$

(3.7)

where  $A_b$  and  $A_i$  denote the area for bin b and cell i;  $D_b$  is bin b's cell density;  $D_t$  is the target density, and  $V_{mov}$  is the set of movable cells. Concretely, each bin b's cell density  $D_b$  in the cell density map  $D \in \mathbb{R}^{M_r \times M_c}$  is defined as,

$$D_b = \frac{\sum_{i \in V} A_i \cap A_b}{A_b}, \ \forall b \in B$$

(3.8)

where  $A_i \cap A_b$  defines the overlap area between cell i and bin b. Similar to [88] and [2], we insert filler cells inside the electrostatic system to handle whitespace and prevent the density objective to overly spread the cells. The inserted filler density map  $D_{fl} \in \mathbb{R}^{M_r \times M_c}$  is given

as,

$$D_{fl,b} = \frac{\sum_{i \in V_{fl}} A_i \cap A_b}{A_b}, \ \forall b \in B,$$

(3.9)

where  $V_{fl}$  denotes the set of filler cells. Therefore the total density map  $\tilde{D} \in \mathbb{R}^{M_r \times M_c}$  used for solving the electrostatic system is formulated as follows,

$$\tilde{D}_b = \frac{\sum_{i \in V \cup V_{fl}} A_i \cap A_b}{A_b} \tag{3.10a}$$

$$= \frac{\sum_{i \in V} A_i \cap A_b}{A_b} + \frac{\sum_{i \in V_{fl}} A_i \cap A_b}{A_b}$$

(3.10b)

$$= D_b + D_{fl,b}, \ \forall b \in B \tag{3.10c}$$

Then, the matrix form of Equation (3.10) is formulated as

$$\tilde{D} = D + D_{fl} \tag{3.11}$$

We observe that both Equation (3.8) and Equation (3.11) contain the computation of cell density map D. Due to the heavy load of the density map operator, performing a common sub-operator extraction in Equation (3.11) will naturally boost the performance. As shown in Figure 3.2(a), we first compute the cell density map D and the filler density map  $D_{fl}$  separately. We then adopt the element-wise add operator to compute the total density map  $\tilde{D}$  and apply the overflow operator to calculate OVFL. Note that overflow ratio computation is needed for updating parameters in each GP iteration. The proposed sub-operator extraction technique will reduce the total computation time of the cell density map D and achieve a visible improvement in the total GPU execution time.

#### 3.3.3 Operator Reduction

PyTorch [104] is a well-known deep learning library that provides a lot of built-in differentiable operators (e.g. element-wise addition, matrix multiplication, convolution, etc.). In forward propagation, users can apply the provided/user-defined operators to construct a neural network or a gradient-based optimization. In backward propagation, an automatic

**Figure 3.2:** Illustration for the operator extraction technique and the cell gradient computation scheme.

differentiation (autograd) engine is invoked to compute derivatives automatically. Although PyTorch makes development convenient, there are technical details that need to be carefully considered when building a global placer using PyTorch.

In PyTorch, the execution of each operator will perform a kernel launching step on CPU before executing the core CUDA kernel on GPU. Not only that the forward propagation will execute operators but also the backward propagation, driven by the autograd engine, need to run gradient operators. However, the kernel launching overheads of these operators may even be much larger than their GPU execution overheads when their computation workloads are small. Except for the heavily loaded operators (e.g. for wirelength and density computations) that are related to the netlist size and the die area, the kernel launching overheads of most other placement operators are much larger than their GPU execution overheads. In this case, the more operators being executed, the larger the total kernel launching overhead there will be. If the total kernel launching overhead dominates the GPU execution time, the speedup will be limited. To this end, we propose a series of techniques to reduce the number of operators to mitigate the problem.

The first technique is to avoid invoking the heavy autograd engine. Since the number of

forward operators are almost the same as that in the backward, invoking the heavy autograd engine will almost double the number of operators and bring large kernel launching overhead on CPU. To resolve this problem, we directly derive the numerical solutions of the wirelength gradient and the density gradient without invoking the autograd engine and assign a weighted accumulated gradient to each cell. This step can reduce the total kernel launching time and boost the performance significantly. It is worth noting that avoiding invoking the autograd engine will not affect our framework's extensibility since PyTorch also supports invoking the autograd engine for user-defined loss function and accumulating the separately computed numerical gradient with the backward gradient of the user defined loss function as illustrated in Figure 3.2(b).

Besides, the PyTorch in-place operators, which directly manipulate on the tensor memory without memory copying, are used as much as possible. This technique will naturally avoid redundant copying.

Finally, as frequent synchronization will interrupt the GPU pipeline and slow down the total run time, we reorder the operators that need synchronization to the end of the execution queue in each GP iteration so that the negative effects of synchronization can be alleviated.

#### 3.3.4 Operator Skipping

It is observed that the ratio between density gradient and wirelength gradient, given as follows,

$$r = \frac{\lambda |\nabla D_{x,y}|}{|\nabla W L_{x,y}|} \tag{3.12}$$

is ultra-small in the early placement stage. Based on the observation, we propose an early-stage operator skipping technique to further boost the runtime performance. When  $(r < 0.01) \land (iteration < 100)$ , the density gradient operator will only be executed once per 20 iterations.

#### 3.3.5 Determinism

Similar to DREAMPlace [80], we convert the floating point numbers to fixed point to avoid non-deterministic floating-point atomic-add operations. To store the converted GPU data, extra memory allocation is needed. We observe that the size of the allocated GPU memory is unchanged in each GP iteration, and dynamical allocation will cause frequent synchronization that interrupts the execution pipeline. Thus we apply a GPU memory pre-allocation technique to avoid redundant synchronization and significantly accelerate the deterministic mode.

## 3.4 Placement-Stage-Aware Parameters Scheduling

Preconditioning is widely used in global placement [88, 78, 59]. Given in Equation (3.13), preconditioning is applied to the optimization objective for reducing the condition number and accelerating Nesterov's optimization convergence.

$$\mathbf{H}^{-1} = (\mathbf{H}_{\mathbf{W}} + \lambda \mathbf{H}_{\mathbf{D}})^{-1}, \tag{3.13a}$$

$$\mathbf{H}_{\mathbf{W}} = \operatorname{diag}(|S_1|, |S_2|, ..., |S_{|V|}|),$$

(3.13b)

$$\mathbf{H_D} = \text{diag}(A_1, A_2, ..., A_{|V|}),$$

(3.13c)

where  $S_i = \{e\}_i$  is the set of nets containing cell i,  $|S_i|$  is the number of nets connecting cell i,  $A_i$  is the area of cell i, and  $\lambda$  is the weight of the density penalty. Recall that the placement objective is formulated as,

$$\min_{p} WL(p) + \lambda D(p).$$

With the preconditioner, the modified cell gradient is derived as follows,

$$\nabla p = (\mathbf{H}_{\mathbf{W}} + \lambda \mathbf{H}_{\mathbf{D}})^{-1} (\nabla W L_{x,y} + \lambda \nabla D_{x,y}), \tag{3.14}$$

where  $\nabla p$  denotes the cells' gradient.

To measure the placement stage, we introduce the precondition weighted ratio  $\omega \in (0,1)$ ,

Figure 3.3: An example of the precondition weighted ratio  $\omega$  of ISPD 2005 adaptec1.

$$\omega(\lambda) = \lambda |\mathbf{H}_{\mathbf{D}}| |\mathbf{H}_{\mathbf{W}} + \lambda \mathbf{H}_{\mathbf{D}}|^{-1}$$

(3.15a)

$$= \frac{\lambda \sum_{i \in V} A_i}{\sum_{i \in V} |S_i| + \lambda \sum_{i \in V} A_i},$$

(3.15b)

where  $|\cdot|$  is the  $L_1$ -norm operator. Note that  $\omega$  is only determined by the variable  $\lambda$  ( $A_i$  and  $S_i$  are only related to the design technology), where  $\lambda$  is gradually updated during placement to enhance the importance of the density objective. Compared to  $\frac{\lambda}{1+\lambda}$ , the precondition weighted ratio  $\omega(\lambda)$  is more relevant to the cell gradient formulated in Equation (3.14) and it further reflects the relative importance of  $\lambda \mathbf{H_D}$  in  $\mathbf{H}^{-1}$ .

Through our investigation,  $\omega(\lambda)$  successfully measures the global placement optimization stage. As shown in Figure 3.3,  $\omega$  gradually increases when the placement iterates.

#### Algorithm 1 Placement-Stage-Aware Parameters Scheduling

```

1: \gamma \leftarrow \gamma_0

2: \lambda \leftarrow \lambda_0

3: while iteration < ITER and NOT Convergence do

if 0.5 < \omega < 0.95 and iteration%3 \neq 0 then

SKIP_UPDATE

5:

6:

\gamma \leftarrow \gamma \times coef(overflow)

7:

\lambda \leftarrow \lambda \times \mu(\Delta hpwl)

\triangleright \gamma and \lambda are derived from [17]

8:

\omega \leftarrow \frac{\lambda |\mathbf{H_D}|}{|\mathbf{H_W}| + \lambda |\mathbf{H_D}|}

9:

```

When  $\omega < 0.05$  (marked in red), the optimization objective is wirelength-dominated, and cells are driven to the position with minimum wirelength. As  $\omega$  rapidly grows in the intermediate stage (0.05 <  $\omega$  < 0.95, marked in blue), cells spread over the whole placement region, and the overlap ratio significantly decreases. At the end of the placement ( $\omega$  > 0.95, marked in yellow), cells are forced to a final position with minimum local penalty at the final stage. Note that the first-order derivatives of  $\omega(\lambda)$  in the red and yellow areas are both small, while that in the blue area is relatively larger.

If we slow down the parameter update in the blue stage, the gradient optimizer will search the solution spaces more fine-grained, and the quality of the final solution will become better. However, a slower update of placement parameters would affect the running time so we only adopt the above slowing update technique when  $0.5 < \omega < 0.95$  (marked in green in Figure 3.3) to exploit the optimization space while saving the runtime. A detailed description of this technique is given by Algorithm 1.

## 3.5 Extending Xplace via Neural Enhancement

In this section, we show Xplace's high extensibility by incorporating a deep neural network into its optimization process. As Xplace has a similar architecture to a normal neural network of PyTorch [104], it is natural and easy to embed a neural network as an extension. Here, we propose a neural-plugged-in framework to explore the possibility of learning-based frameworks. We also demonstarte such extension can further improve Xplace's solution

quality.

Neural networks have shown great potential on mapping between dynamic systems defined by partial differential equations (PDE). Previous works of image-to-image mapping tasks are usually conducted in the spatial domain and are accurate on training datasets. However, when given a new pattern of instance, they do not perform well. Recently, convolution operation in the frequency domain is discovered to be more powerful in generalizing dynamic systems determined by a family of partial differential equations [69]. Such Fourier-Neural-Operator (FNO) is capable of learning the universal solution of a dynamic system with only limited training data.

In the global placement problem, the function of the electric field Equation (3.5) solved by Poisson's equation can be modeled as a dynamic system mapping from electron distribution to electric field, in which electron distribution is the 2-D density map of placement and the electric field is the unit moving force on x and y-axis.

As illustrated in Figure 3.4, our model is a two-path convolution network consisting of a spatial-domain path (blue) to extract the explicit information of a specific feature map and a frequency-domain path (orange) to generalize the global information of a continuous dynamic system. In order to transfer the model to multi-resolution, the input density map D is concatenated with mesh-grid index  $M_X(x,y) = \frac{x}{X}$  and  $M_Y(x,y) = \frac{y}{Y}$ , where X and Y are map sizes. The input map  $I = \{D; M_X; M_Y\}$  is firstly lifted to multi-channel by a fully-connected layer, denoted as  $I_m = FC(I)$ , and then fed into two paths.

In the Fourier path, the spatial map is transformed into the frequency space after Fast-Fourier-Transform (FFT) function  $\mathcal{F}$ . A low-pass-filter (LPF) L preserves a number of lower frequency components and then a linear transformation  $\mathcal{W}$  is applied to the filtered map. After applying an Inverse-Fast-Fourier-Transform (IFFT) function  $\mathcal{F}^{-1}$ , the frequency map is transformed back to the spatial domain,

$$Freq_{layer}(I_m) = \mathcal{F}^{-1}(\mathcal{W}^T \cdot L(\mathcal{F}(I_m)))$$

(3.16)

In the spatial path, a simple pixel-wise convolution layer is operated on the feature map.

Figure 3.4: Neural-network plugged-in placement extension.

Maps from two paths are added followed with a nonlinear activation function *GELU*. The above process of a FNO is described as

$$\mathcal{O}(I_m) = GELU\Big(Conv_{2D}(I_m) + Freq_{layer}(I_m)\Big)\Big)$$

(3.17)

We then get the output after a down-sampling fully-connected layer  $FC^{-1}(\mathcal{O}(I_m))$  and a relative  $L_2$  loss function is used for back-propagation:

$$L_2(\mathbf{x}_i, f(\mathbf{x}_i; \theta)) = ||f(\mathbf{x}_i, \theta) - \mathbf{y}_i||_2 / ||\mathbf{y}_i||_2$$

(3.18)

where  $\mathbf{x}_i$ ,  $\mathbf{y}_i$ , f and  $\theta$  are the i-th input, label, network model and network parameters. The label and prediction are normalized for evaluation.

In this model, we do not need to collect the ground-truth training data from real placement benchmarks. Rather, we can generate randomly distributed density maps and compute the numerical solution of the corresponding electric fields which will be used as labels for training.

Since we do a pixel-wise convolution on the spatial maps, the resolution of the input maps will not affect the convolution results. Moreover, in Fourier space, low-frequency components describe the global information, while high-frequency components describe the explicit local information. That means, a low-resolution image and a high-resolution image will share similar low-frequency components, with differences in high-frequency components only. As we only preserve a certain number of lower-frequency components, our model is resolution-independent. The model can be trained on low-resolution data and extended to high-resolution, which improves the adaptability of the model.

The electric fields on both the x and y directions share the same partial differential function, with only a difference in the direction. Therefore the model can be trained in only one direction and still be workable in the other direction by simply flipping the input feature map, further improving the generalization of this model.

As the model is trained on low-resolution data and only preserves lower-frequency components, the predicted density gradient will have a good global view to spread cells. Thus we insert the nn-predicted density gradient  $\nabla_{nn}D_{x,y}$  into the early stage of placement to help push cells around. With the precondition weighted ratio  $\omega$  defined in Section 3.4 and the gradient ratio r defined in Section 3.3.4, a smooth function  $\sigma(r,\omega)$  is used to weighted-sum with the numerical solution of the density gradient, given as follows,

$$\sigma(r,\omega) = \frac{1}{1 + e^{-5(r/0.005 - 0.5)}} - \frac{1}{1 + e^{-5(\omega/0.05 - 0.5)}}$$

(3.19)

$$\nabla' D_{x,y} = (1 - \sigma) \nabla D_{x,y} + \sigma \nabla_{nn} D_{x,y}$$

(3.20)