# Building up End-to-end Mask Optimization Framework with Self-training

Bentian Jiang CSE Department, CUHK btjiang@cse.cuhk.edu.hk

Lixin Liu CSE Department, CUHK lxliu@cse.cuhk.edu.hk

#### ABSTRACT

With the continuous shrinkage of device technology node, the tremendously increasing demands for resolution enhancement technologies (RETs) have created severe concerns over the balance between computational affordability and model accuracy. Having realized the analogies between computational lithography tasks and deep learning-based computer vision applications (e.g., medical image analysis), both industry and academia start gradually migrating various RETs to deep learning-enabled platforms. In this paper, we propose a unified self-training paradigm for building up an endto-end mask optimization framework from undisclosable layout patterns. Our proposed flow comprises (1) a learning-based pattern generation stage to massively synthesize diverse and realistic layout patterns following the distribution of the undisclosable target layouts, while keeping these confidential layouts blind for any successive training stage, and (2) a complete self-training stage for building up an end-to-end on-neural-network mask optimization framework from scratch, which only requires the aforementioned generated patterns and a compact lithography simulation model as the inputs. Quantitative results demonstrate that our proposed flow achieves comparable state-of-the-art (SOTA) performance in terms of both mask printability and mask correction time while reducing 66% of the turn around time for flow construction.

### **CCS CONCEPTS**

• Hardware  $\rightarrow$  Design for manufacturability.

#### **KEYWORDS**

Mask Optimization; Optical Proximity Correction; Deep Learning

#### **ACM Reference Format:**

Bentian Jiang, Xiaopeng Zhang, Lixin Liu, and Evangeline F.Y. Young. 2021. Building up End-to-end Mask Optimization Framework with Self-training. In *Proceedings of the 2021 International Symposium on Physical Design (ISPD '21), March 22–24, 2021, Virtual Event, USA*. ACM, New York, NY, USA, 8 pages. https://doi.org/10.1145/3439706.3447050

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

ISPD '21, March 22–24, 2021, Virtual Event, USA © 2021 Association for Computing Machinery. ACM ISBN 978-1-4503-8300-4/21/03...\$15.00 https://doi.org/10.1145/3439706.3447050

Xiaopeng Zhang CSE Department, CUHK xpzhang@cse.cuhk.edu.hk

Evangeline F.Y. Young CSE Department, CUHK fyyoung@cse.cuhk.edu.hk

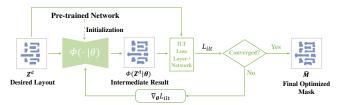

Figure 1: DNN-ILT, a typical end-to-end on-neural-network ILT correction (mask optimization) framework [1].

#### 1 INTRODUCTION

The mismatches between lithography system wavelengths and ever-shrinking device feature sizes lead to inevitable distortion effects on the printed patterns. In the past two decades, industry has relied more on the computational lithography simulation models and resolution enhancement techniques (RETs) to guarantee the functionality and high-volume yields for complex circuit designs in advanced technology nodes.

Under the guidance of rigorous and compact lithography simulation models, RETs, including but not limited to, optical proximity correction (OPC), sub-resolution assist feature (SRAF) insertion, phase-shifting masks (PSM), etc., aim to help all on-mask patterns achieving proper exposures. As one of the most prevailing RETs, current mainstream OPC compensates the printed image errors (caused by non-linear effects, optical diffraction and interference effects, resist, etc.) by modifying the on-mask features with either empirical or numerical approaches.

Empirical OPC approach usually refers to rule-based OPC, where for a given lithography process, the corrections are made empirically by modifying the features according to a set of pre-determined rules [2]. Rule-based OPC is extremely fast, but only suitable for less complex designs due to its faltering accuracy and robustness for advanced technology nodes. Starting from sub-90nm generation, industry began to switch to forward model-based OPC, where the predicted resist image from a compact lithography simulator drives the movements of the on-mask feature edges iteratively until a preset tolerance of printing error is met [2]. Model-based OPC has been adopted ubiquitously for 193i layers since it achieves a reasonable balance between model accuracy and computational overhead. On the other hand, the numerical OPC approach, which is also referred as inverse lithography technique (ILT), treats OPC as an inverse imaging problem and performs pixel-wise mask optimization by gradient descent to search for the optimum mask shape yielding the desired resist shape. ILT correction is more aggressive

and is able to achieve the best possible process window obtainable for 193i layers [3], and recent study shows even EUV patterning for sub-7nm also has similar demands for ILT-style corrections [4].

Apparently, the effectiveness of either model-based OPC or ILTbased correction heavily relies on the accuracy of the lithography simulation model. Among various computational simulation recipes, rigorous lithography simulation is accomplished by solving Maxwell's equations for the electromagnetic field (EMF) with rigorous EMF solvers such as rigorous coupled wave analysis (RCWA), finite-difference time-domain (FDTD) and pseudo-spectral timedomain (PSTD) [5]. Rigorous lithography simulation is capable of modeling the mask topography effects (3D mask effects), aerial imaging and resist development. Despite their superior accuracy, performing full-chip rigorous simulations in every iteration of the OPC process is generally not practical. In contrast to rigorous models, compact lithography simulation models combine a reasonably accurate and physically correct aerial imaging model (e.g., solving partially coherent imaging calculations with Hopkins approach) with a simple resist model [2] (e.g., a constant or variable threshold resist model). In practice, integrating compact lithography simulation models into model-based OPC and ILT generally can be regarded as a compromising solution to trade-off between result quality and computational affordability.

Inspired by the analogies between lithography imaging and typical deep learning-based computer vision applications such as medical imaging, deep neural networks (DNNs) has prevalently become a proper alternative to carry out various lithographic-related tasks, which includes (1) approximating rigorous lithography simulations on 3D mask-aware aerial imaging [6, 7] and resist effects modeling [8]; (2) performing end-to-end mask optimization on deep learning platforms [1, 9, 10]; (3) applying DNNs on fast early stage hotspots detection [11], etc. Among them, Ye et al. [6] proposes a generative learning-based framework which is capable of predicting 3D aerial images with accurate modeling of the mask topography effects while achieving orders of magnitude speedup. Jiang et al. [1] casts a compact lithography simulation model as a neural network layer and hereby converts the ILT correction process as a DNN training procedure to achieve end-to-end mask optimization. Liu et al. [10] pre-trains multiple DNN-based rigorous lithography simulators (DRLS) for modeling 3D mask effects, aerial imaging and resist effects, these DRLSs are then integrated into the mask synthesis flow for guiding the entire mask optimization process.

As proof-of-concept (POC) studies, the above seminal works have successfully verified the feasibility and significant runtime superiority of leveraging deep learning paradigm to carry out computational lithographic tasks. However, there are still gaps between POC evaluations and realistic massive deployments. On one hand, academia researchers can hardly obtain the opportunity to evaluate ideas using industrial resources (e.g., design layouts and lithography simulation recipes) without restrictive permissions. As a result, some recent works from academia [1, 6, 8, 9, 12–14] are still widely using legacy problem settings or evaluating on contact-layers only, which may not be able to reflect the newest demands from industry. On the other hand, implementing numerical optimization flow such as ILT from scratch is generally time-consuming. Extensive efforts, including fine-tuning the parameters, enabling proper parallelism, polishing the efficiency optimizer, etc. (which are well-developed

features in deep learning toolkits), are required to achieve a reasonable performance.

In accordance with these observations, we are aiming at finding a unified solution for above concerns by fully leveraging the efficiency of off-the-shelf deep learning software and hardware, and achieves reasonably good performance with breakthough reduction on the development overheads. In this paper, we presented a unified self-contained training paradigm for building up an end-to-end learning-based mask optimization framework from scratch (a typical flow is shown in Figure 1). Our proposed flow makes use of (1) a learning-based pattern generation stage to massively synthesize diverse and realistic layout patterns following the distribution of the undisclosable target layouts, while keeping these confidential layouts blind for any successive training stage, and (2) a complete self-training stage for building up an end-to-end learning-based mask optimization framework from scratch, which only requires the aforementioned generated patterns and a compact lithography simulation model as the inputs.

To the best of knowledge, this is the first work that attempts to systematically build up an end-to-end mask optimization flow entirely on deep learning platform (i.e., PyTorch) without any pre-labelled data. Note that, the only open-sourced industrial package (with 32nm or below tech node) available for us is from ICCAD 2013 mask optimization contest [15]. Considering such limitation, we perform all evaluations based on the compact lithography simulation model and benchmarks provided by them. Nevertheless, the proposed concept is a unified paradigm for fab and vendor as it can be naturally migrated to rigorous simulation environment by replacing the compact lithography simulation model with other DRLSS [10]. Our key contributions are highlighted as follows.

- We build up an end-to-end learning-based mask optimization framework from scratch (completely on deep learning platform) with the self-training scheme.

- A generative learning-based pattern generator is applied to massively synthesize diverse layout patterns while preserving the major characteristics of the given confidential layouts. A simple third-party reverse attack is also performed to empirically study the effectiveness of the generator for protecting the confidential layouts from disclosure.

- Our self-training scheme does not required any pre-labelled mask data. Only a set of generated patterns and a compact litho-simulation model are needed as the inputs.

- Experimental evaluation demonstrate that our proposed flow achieves comparable SOTA performance in terms of both mask printability and mask correction time while reducing 66% of the turn around time for flow construction.

The rest of the paper is organized as follows. Section 2 lists some preliminaries. Section 3 discusses the details of the framework and algorithms. Section 4 presents experimental results, followed by a conclusion in Section 5.

#### 2 PRELIMINARIES

In this section, we will provide preliminaries for the background and formulate the problem. For convenience, notations used in this paper are listed in table 1.

| $Z^{ m d}$                             | Desired target layout                                                   |  |  |  |

|----------------------------------------|-------------------------------------------------------------------------|--|--|--|

| М                                      | Optimized mask                                                          |  |  |  |

| I                                      | Aerial images                                                           |  |  |  |

| $R_{\text{nom}}$                       | Nominal process condition: nominal dose and focus                       |  |  |  |

| $R_{\text{max}}$                       | $\mid$ Max process condition: max dose and nominal focus $H$            |  |  |  |

| $R_{\min}$                             | Min process condition: min dose and defocus $H_{ m def}$                |  |  |  |

| $Z$ , $Z_{\rm in}$ , $Z_{\rm out}$     | Binary wafer image under the $R_{ m nom}$ , $R_{ m min}$ , $R_{ m max}$ |  |  |  |

| Н                                      | A set of optical kernels $\{\boldsymbol{h}_1,\ldots,\boldsymbol{h}_K\}$ |  |  |  |

| 8                                      | Convolution operator                                                    |  |  |  |

| $f(\cdot \mid R)$                      | Lithography simulation under a process condition R                      |  |  |  |

| $\Phi(\cdot \mid \boldsymbol{\theta})$ | Neural network forward function with weights $	heta$                    |  |  |  |

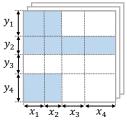

$\delta_x = \begin{bmatrix} x_1 & x_2 & x_3 & x_4 \end{bmatrix}$  $\delta_y = \begin{bmatrix} y_1 & y_2 & y_3 & y_4 \end{bmatrix}$

(a) Splitting original pattern

(b) Squish topology and geometry

Figure 2: Squish pattern representation.

#### 2.1 Compact Lithography Simulation Model

A compact lithography model combines a reasonably accurate and physically correct aerial imaging model with a very simple resist mode [2]. In practice, Hopkins' approach is widely used for modeling the partially coherent lithography systems (193i system with annular illumination in this work), where an approximate solution to the Hopkins imaging equations called Sum of Coherent Sources (SOCS) can be applied to calculate the aerial image. Theoretically, the aerial image can be obtained by convolving the mask  $\boldsymbol{M}$  with a set of pre-computed coherent convolution kernels  $\boldsymbol{H}$  and taking the weighted summation with corresponding coefficients  $\boldsymbol{\omega}$ :

$$\boldsymbol{I}(x,y) = \sum_{k=1}^{\infty} \omega_k |\boldsymbol{M}(x,y) \otimes \boldsymbol{h}_k(x,y)|^2 \approx \sum_{k=1}^{N} \omega_k |\boldsymbol{M}(x,y) \otimes \boldsymbol{h}_k(x,y)|^2, \tag{1}$$

where  $h_k$  and  $\omega_k$  are the  $k^{th}$  kernel and weight. As the coefficients quickly decaying to zero, the infinite summation will be cut off at some number N, where N=24 in our implementation. The constant threshold resist (CTR) model is then used to model the resist action for developing the final binary wafer image Z. It is described with a step function  $\Gamma(\cdot)$ :

$$Z(x,y) = \Gamma(I(x,y)) = \begin{cases} 1, & \text{if } I(x,y) \ge I_{th}, \\ 0, & \text{if } I(x,y) < I_{th}, \end{cases}$$

(2)

where  $I_{th} = 0.225$  is a constant in our implementation.

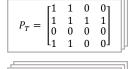

Figure 3: A typical pattern topology generation flow [16].

#### 2.2 Learning-based Pattern Generation

To produce diverse new patterns, we apply the approach in [16], a generative learning-based pattern generation framework for pattern topology generation and legalization. This approach has the capability of learning inherent distributions of two-dimensional layouts and generate realistic patterns.

In [16], the layout patterns are firstly converted to squish pattern representation composed of a topology matrix and two geometry vectors (as shown in Figure 2). The topology matrix contains most of the information of a layout pattern and serves as the input of the neural networks in [16].

As depicted in Figure 3, the pattern topology generation model has an encoder-reparameterization-decoder pipeline for feature learning and pattern reconstruction. In the training stage, the encoder  $E^G$  maps a pattern topology P into a Gaussian space with mean  $\mu$  and variance  $\sigma^2$ . Then the reparameterization block samples a latent vector l by  $l=\mu+\sigma\odot\varepsilon$ , where  $\varepsilon$  follows a standard normal distribution, i.e.,  $\varepsilon\sim \mathcal{N}(0,l)$  and  $\odot$  signifies an element-wise product. After that, the decoder  $D^G$  converts the latent vector l back into the pattern topology space and reconstructs a topology P' that are expected to be close to P. The objective function of training is as follows:

min

$$D_{KL}(\mathcal{N}(\mu, \sigma^2) || \mathcal{N}(0, I)) + \lambda || \mathbf{P} - \mathbf{P}' ||_F^2,$$

(3a)

s.t.

$$\mu = f_R^{\mu}(\tilde{l}, W_R^{\mu}), \quad \sigma = f_R^{\sigma}(\tilde{l}, W_R^{\sigma}),$$

(3b)

$$\tilde{l} = E^G(P, W_E), \quad l = \mu + \sigma \odot \varepsilon, \quad \varepsilon \sim \mathcal{N}(0, I), \quad (3c)$$

$$P' = D^G(l, W_D). (3d)$$

The  $D_{KL}$  in Equation 3a represents the Kullback-Leibler (KL) divergence which measures the difference between the distribution  $\mathcal{N}(\mu,\sigma^2)$  and a standard Gaussian distribution  $\mathcal{N}(0,I)$ .  $\tilde{l}$  is an internal representation of the output from the encoder, while l is a sampled latent vector with Gaussian distribution from the reparameterization block. Besides,  $W_R^\mu, W_R^\sigma, W_E$  and  $W_D$  represent the trainable weights associated with the respective units.

In the topology generation stage, the latent vector l in Gaussian space allows perturbation by adding a random Gaussian vector  $\Delta l$ , as shown in Figure 3. Apparently the new vector  $l + \Delta l$  is still in Gaussian distribution, which implies it can be converted back to the pattern topology space by the trained decoder  $D^G$  and generate a new pattern topology with Equation 4:

$$P' = D^G(l + \Delta l, W_D), \quad \Delta l_i \sim \mathcal{N}(0, c^2), \quad i = 1, ..., K,$$

(4)

where  $\triangle l$  is sampled from a Gaussian distribution with mean 0 and variance  $c^2$ . The  $c^2$  is a user-defined parameter that controls the range of perturbation. where  $c^2$  is set to 0.5 in our implementation.

## 2.3 End-to-end Learning-based Mask Optimization by ILT

As depicted in Figure 1, DNN-ILT is a typical end-to-end on-neuralnetwork ILT correction framework [1] which consists of (1) a pretrained backbone neural network to perform layout-to-mask translation, (2) an ILT correction layer to calculate ILT loss and corresponding gradient, and (3) other customized layers for optimizing user-specific objectives (e.g., process variation band).

In DNN-ILT, a compact lithography simulation model (section 2.3) is re-implemented for GPU with CUDA. The CUDA-based lithosimulator is then used to implement an ILT correction layer, where its forward function calculates the forward propagation ILT loss:

$$L_{\text{ilt}}(Z^{\text{d}} \mid \theta) = ||Z - Z^{\text{d}}||_{2}^{2} = ||f(\Phi(Z^{\text{d}} \mid \theta) \mid R_{\text{nom}}) - Z^{\text{d}}||_{2}^{2}, \quad (5)$$

and the backward function computes the backward propagation ILT gradient  $\nabla_M L_{\mathrm{ilt}} = \frac{\partial L_{\mathrm{ilt}}}{\partial M}$  with respect to mask M. Since the predecessor backbone network's forward prediction  $\Phi(Z^{\mathrm{d}}|\theta)$  yields a mask M (we omit the sigmoid approximation here for simplicity), its weights  $\theta$  can be updated accordingly through the chain rule  $\nabla_{\theta} L_{\mathrm{ilt}} = \frac{\partial L_{\mathrm{ilt}}}{\partial M} \frac{\partial M}{\partial \Phi(Z^{\mathrm{d}}|\theta)} \frac{\partial \Phi(Z^{\mathrm{d}}|\theta)}{\partial \theta}$ .

As a consequence, given a desired target layout  $\mathbf{Z}^{d}$  as input, the on-neural-network ILT correction process is essentially an unsupervised training procedure for the backbone network to minimize the ILT loss in Equation (5). This is an end-to-end procedure, since the mask optimization process will be performed iteratively until the preset tolerance is met.

#### 2.4 Term Definitions

We further define some concepts used in this paper to highlight the features of our proposed flow.

- 2.4.1 Semi-supervised Learning. Semi-supervised learning (SSL) is a learning paradigm concerned with the design of models using a small amount of labeled data in conjunction with a large amount unlabeled data for training [17].

- 2.4.2 Self-training. Self-training can be regarded as a wrapper method for semi-supervised learning [17]. Considering the labelled dataset with m samples  $L = \{(x^1, y^1), (x^2, y^2), ..., (x^m, y^m)\}$  where  $x^i \in \mathbb{X}, y^i \in \mathbb{Y}, \ \forall i \in \{1, ..., m\}, \ \text{and an unlabelled dataset with } l$  samples  $U = \{x^{m+1}, x^{m+2}, ..., x^{m+l}\}$ , where l >> m. Self-training aims to seek a mapping  $\Phi : \mathbb{X} \to \mathbb{Y}$  by repeating the followings:

- (1) Train a model  $\Phi$  from set L.

- (2) Apply  $\Phi$  to predict the pseudo-labels of k samples in set U.

- (3) Remove the predicted k samples from set U and add them to set L, until there is no sample in set U.

- 2.4.3 Complete Self-training. In this paper, we further extend the concept of self-training to complete self-training. In contrast to classic self-training, we add two more features to complete self-training:

- (1) The input training dataset for complete self-training paradigm **only contains unlabelled** data.

- (2) In contrast to directly generating the pseudo-labels for unlabelled samples by the network inference, the complete

self-training paradigm produces labels by performing unsupervised training on the network itself.

#### 2.5 Problem Formulation

The ultimate goal for OPC (mask optimization) is to enhance the mask printability, which can be measured by squared L<sub>2</sub> error and process variation band (PVBand).

**Definition 1** (Squared L<sub>2</sub> Error). Given the desired target layout  $Z^d$  and the wafer image Z of a mask M where  $Z = f(M \mid R_{\text{nom}})$ , the squared L<sub>2</sub> error is given by  $||Z - Z^d||_2^2$ .

**Definition 2** (Process Variation Band). Process variation band (PVBand) denotes the contour area variations under  $\pm 2\%$  dose error, which is measured by the summation of bitwise-XOR between  $Z_{\text{in}} = f(M \mid R_{\text{min}})$  and  $Z_{\text{out}} = f(M \mid R_{\text{max}})$ .

**Problem 1** (End-to-end Learning-based Mask Optimization). Given an undisclosable layout pattern set  $\mathfrak{Z}^u$ . Build up an end-to-end learning-based ILT correction framework for  $\mathfrak{Z}^u$  without directly involving  $\mathfrak{Z}^u$  in the training. The constructed framework should be able to generate optimized mask solutions for testing layouts to simultaneously minimizes (1) squared L2 error, (2) PVBand and (3) turn around mask optimization time.

#### 3 PROPOSED FLOW

#### 3.1 Overview

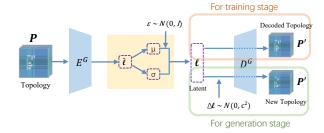

Figure 4 presents the overall flow of how to build up an end-toend learning-based mask optimization framework from scratch. Our proposed flow consists of two stages, (1) a pattern generation stage that applies a generative learning-based model to sample from the distribution of a given realistic but confidential layouts and to massively synthesize diverse fake layouts with similar characteristics (Figure 4(b)); and (2) a complete self-training stage that only leverages the aforementioned generated fake layout patterns and a GPU-based compact lithography simulation model to construct an entire on-neural-network ILT correction (DNN-ILT) framework from scratch (Figure 4(a), (c), (d), (e)).

As depicted in Figure 4, given an undisclosable layout pattern set  $\mathcal{Z}^u$ , the pattern generation stage first synthesizes a new layout pattern set  $\mathcal{Z}^d$  following the distribution of  $\mathcal{Z}^u$  (i.e., similar design style and design space coverage). We then split  $\mathcal{Z}^d$  into T batches

randomly, i.e.,  $\mathcal{Z}^{\text{d}} = \bigcup_{i=1}^{T} \mathcal{Z}_{i}^{\text{d}}$ . At the self-training stage, the  $t^{\text{th}}$  batch

of generated layout patterns  $\mathcal{Z}_t^d$  is fed to the DNN-ILT self-training procedure at  $t^{th}$  iteration, through which the mask labels  $\tilde{\mathcal{M}}_t^d$  for  $\mathcal{Z}_t^d$  is generated by performing on-neural-network ILT correction (Section 2.3) using our pre-trained backbone model  $\theta_{t-1}$  obtained from the last iteration, and  $(\mathcal{Z}_t^d, \ \tilde{\mathcal{M}}_t^d)$  are then leveraged to pre-train a new backbone model  $\theta_t$  in preparation for the DNN-ILT self-training at the  $(t+1)^{th}$  iteration. This DNN-ILT self-training procedure (Figure 4(c)) is conducted in an iterative manner until all the batches in  $\mathcal{Z}^d$  are consumed and the final output model  $\theta_{pt}^*$  is deployed for testing. As a result, the self-training stage is able to construct an end-to-end learning-based mask optimization framework (based on  $\theta_{pt}^*$ ) from scratch with an unlabelled fake pattern set  $\mathcal{Z}^d$  without seeing any confidential pattern in set  $\mathcal{Z}^u$ .

#### (a) General Pipeline for Self-Training to Build up DNN-ILT from Scratch **Best Pre-trained** Initialize with DNN-ILT DNN-ILT DNN-ILT Model Params Tuning: Self Self-train Self-train Self-train DNN-ILT Model Reconstruction $\boldsymbol{\theta}_{pt}^{*}$ Generated New Patterns: $z_2^d$ $\mathcal{Z}_{T-1}^d$ $Z_1^d$ $Z_T^d$ $\mathcal{P}'$ (c) DNN-ILT Self-train at Iteration t (b) Patterns Generation Many iteration Disclosable DNN-ILT Self-train $\Delta l$ zP Model ILT Model Confidential $E^G D^G$ $G^L$ Params Labels DNN-ILT Params Pre-train Procedure $\boldsymbol{\theta}_t$ $\widetilde{\mathcal{M}}_t$ Real Topologi Design Rules New Topologies Existing Patterns $\delta_x = [x_1, x_2, \dots, x_n]$ $\delta_y = [y_1, y_2, \dots, y_m]$ New Patterns $\mathbf{Z}_{t}^{d} = [\mathbf{Z}_{t,1}^{d}, \mathbf{Z}_{t,2}^{d}, ..., \mathbf{Z}_{t,k}^{d}]$ (e) Extract Squish Patterns from Layouts (r) Reconstruct Layouts (d) DNN-ILT Labeling at Iteration t (e) Pre-train Procedure at Iteration t $\theta_{t-1}$ $L_{ilt}$ Init $\Phi(\mathbf{Z}_{t,i}^d|\boldsymbol{\theta})$ $\widetilde{\boldsymbol{M}}_{t.i}$ $\boldsymbol{Z}_{t,i}^d$ i<sup>th</sup> Desired Layout i<sup>th</sup> ILT Label Intermediate Label $\nabla_{\theta} L_{ilt}$

Figure 4: The self-training paradigm for constructing end-to-end learning-based mask optimization framework from scratch.

However, we are going to show that, it is capable of handling end-to-end mask optimizations for layouts from  $\mathbb{Z}^u$ , since  $\mathbb{Z}^d$  is synthesized following the distribution of  $\mathbb{Z}^u$ .

In the rest of this section, we will present the algorithmic details of the proposed flow.

# 3.2 Learning-based Pattern Generation and Third-party Reverse Attack

3.2.1 Learning-based Pattern Generation. The primary objective of integrating a generative learning-based pattern generation model is to massively synthesize diverse fake layout patterns while preserving the characteristics of the given confidential realistic layouts (i.e., similar design style and design space coverage), and those useful characteristics can hopefully be captured by the later training procedures using directly the generated layouts, thereby maintaining the confidentiality of the undisclosable layouts to other third-party applications (mask optimization in our case).

As depicted in Figure 4(b), this forward pattern generation process can be achieved with the topology generation-legalization pipeline. Given an undisclosable layout pattern set  $\mathbb{Z}^u$ , the corresponding squish-representation set, which consists of a pattern topology set  $\mathbb{P}$  and a geometry vector set  $\delta$ , can be extracted accordingly. The encoder-reparameterization-decoder pipeline (Section 2.2) can be trained by the pattern topology set  $\mathbb{P}$  with the

objective of minimizing the loss in Equation (3). By introducing the random perturbations  $\Delta \boldsymbol{l} \sim \mathcal{N}(0,c^2)$  on each latent vector  $\boldsymbol{l}$  (an internal representation before decoding), a set of new pattern topologies can be generated by the decoder  $D^G$  as  $\mathcal{P}' = D^G(\boldsymbol{l} + \Delta \boldsymbol{l}, W_D)$ . The new pattern topology set  $\boldsymbol{P}'$  will further go through the design rules legalization stage (please refer to [16]). Finally, the newly generated pattern set  $\mathcal{Z}^d$  can be uniquely reconstructed by combining the legalized topology set  $\mathcal{P}''$  and geometry vector set  $\boldsymbol{\delta}$ .

The capabilities of this generative learning-based model for preserving similar design style and design space coverage have been quantitatively verified in [16]. From the perspective of layout owner, the reversibility of these fake patterns to retrieve the original true patterns emerges as a critical concern. To what extent can the generated patterns  $\mathbb{Z}^d$  prevent the mother templates  $\mathbb{Z}^u$  from being re-constructed?

3.2.2 Backward Third-party Attack. We empirically study the reversibility of the pattern generation process through a hacking heuristic under the assumption that all the associated generative models belong to the patterns owner, and **only** the generated patterns  $\mathbb{Z}^d$  are exposed to other end-users. Observing that the geometry vectors remain unchanged during the pattern generation process, recovering an undisclosable layout  $Z^u$  is essentially to recover the corresponding  $P^u$  from its generated topologies  $\mathbb{Y}'_u$ . Apparently, when we have sufficiently large number of randomly

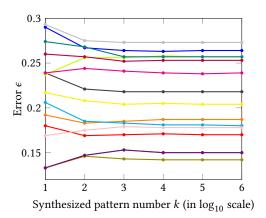

Figure 5: Errors of reverse attacks on 15 samples layout patterns are getting converged with respect to the growth of synthesized patterns.

perturbed latent vectors, the difference between the mean of  $l'_u$  and  $l_u$  will be vanished, and hereby recover the  $P^u$ , that is, as  $k \to \infty$ ,

$$D^{G}(\frac{\sum_{i=1}^{k} l'_{\mathbf{u},i}}{k}, W_{D}) = D^{G}(\frac{\sum_{i=1}^{k} (l_{\mathbf{u}} + \Delta l_{i})}{k}, W_{D}) = D^{G}(l_{\mathbf{u}}, W_{D}) = P^{\mathbf{u}},$$

(6)

where  $\Delta l_i \sim \mathcal{N}(0, c^2)$ ,  $\forall i \in \{1, ..., k\}$ . Inspired by this observation, a hacking heuristic in the view of a third-party user can be described as follows to reversely attack the disclosed generated patterns  $\mathcal{Z}^d$ : (1) extract the corresponding topology matrix set  $\mathcal{P}'$  and geometry vectors set  $\delta$ ; (2) assign all topology matrices with the same  $\delta$  into a batch; (3) for each batch, calculate the mean topology matrix and combine it with  $\delta$  to reconstruct the pattern.

Note that we omit the design rules legalization steps in Figure 4(b) due to the hardness of modeling the complicated legalization behaviors in [16]. In general, legalization steps introduce more nonlinearities which may further hinder the pattern reversibility.

We simulate this attack on 15 sample layouts following the design specifications for 32nm M1 layout topologies provided in ICCAD 2013 mask optimization contest [15], and measure the reconstruc-

tion error  $\epsilon$  by  $\epsilon = \frac{||\frac{\sum_{i=1}^k P_i'}{k} - P||_F}{||P||_F}$ , where for each undisclosable pattern topology P,  $k = \{10, 10^2, ..., 10^6\}$  is the number of synthesised pattern topologies P' exposed to the attacker. Quantitative results are shown in Figure 5. We can see that, the reconstruction error  $\epsilon$  for each sample layout topology P converges when the number of synthesized patterns increases, but **none** of these attacks has achieved a sufficiently small  $\epsilon$  at convergence. Such phenomenon indicates that some biases (unknown for the end-users) may be introduced by the nonlinear decoding procedure  $D^G$  in the layout pattern generator, and as a result, the property in Equation (6) does not follow accurately.

#### 3.3 Complete Self-training Paradigm

As mentioned in Section 2.3, the end-to-end on-neural-network ILT correction process (DNN-ILT) is essentially an unsupervised training procedure of a pre-trained backbone network  $\theta$  for minimizing the ILT loss

$$L_{\mathrm{ilt}}(\boldsymbol{Z}^{\mathrm{d}}\mid\boldsymbol{\theta}) = ||\boldsymbol{Z} - \boldsymbol{Z}^{\mathrm{d}}||_{2}^{2} = ||f(\boldsymbol{\Phi}(\boldsymbol{Z}^{\mathrm{d}}|\boldsymbol{\theta})\mid\boldsymbol{R}_{\mathrm{nom}}) - \boldsymbol{Z}^{\mathrm{d}}||_{2}^{2},$$

where  $Z^d$  denotes the desired target layout,  $f(\cdot \mid R)$  is lithography function under a nominal process condition, and  $\Phi(\cdot \mid \theta)$  is forward prediction of model  $\theta$ . Apparently, the backbone network  $\theta$  is capable of conducting the layout-to-mask translation for DNN-ILT, while different pre-trained backbone networks  $\theta_{\rm pt}$  will yield different **initial** mask predictions for DNN-ILT.

According to the studies in [1], two major motivations drive us to perform ILT correction on a pre-trained neural network.

- (1) Comparing to conventional ILT, DNN-ILT possesses higher searching efficiency (with DL platforms built-in optimizers) and significantly larger search space (optimizing network neurons vs. optimizing binary on-mask pixels), which enable effective numerical optimization.

- (2) ILT is generally sensitive to initial solution quality. A well pre-trained model  $\theta_{pt}$  is capable of predicting a better initial mask solution which helps to achieve faster and better convergence.

However, the DNN-ILT described in [1] still suffers from the extremely time-consuming data-preparation stage during the flow construction, since its backbone model is pre-trained purely in a supervised manner, where all the mask labels are synthesized by a conventional ILT tool [18]. In contrast to this approach, which constructs DNN-ILT via supervised-learning, our complete self-training paradigm aims to build up DNN-ILT from scratch without any pre-labelled mask data and hereby "eliminate" the need of a conventional data-preparation procedure.

As depicted in Figure 4(a), the pipeline of our complete self-training stage consumes T iterations of DNN-ILT self-training processes (Figure 4(c)) to produce the final pre-trained backbone model  $\theta_{\mathrm{pt}}^*$  for DNN-ILT. At the  $t^{\mathrm{th}}$  DNN-ILT self-training iteration, the  $t^{\mathrm{th}}$  batch of target layout set  $\mathcal{Z}_t^{\mathrm{d}}$  is fed to DNN-ILT to generate the corresponding mask labels  $\tilde{\mathcal{M}}_t^{\mathrm{d}}$  that can minimize the following mask printability loss,

$$\begin{split} L_{\text{msk\_print}} = & \alpha \cdot L_{\text{ilt}} + \beta \cdot L_{\text{pvband}} \\ = & \alpha \cdot ||f(\Phi(\mathcal{Z}_t^d | \boldsymbol{\theta}_{t-1}) \mid \boldsymbol{R}_{\text{nom}}) - \mathcal{Z}_t^d||_2^2 + \\ & \beta \cdot ||f(\Phi(\mathcal{Z}_t^d | \boldsymbol{\theta}_{t-1}) \mid \boldsymbol{R}_{\text{min}}) - f(\Phi(\mathcal{Z}_t^d | \boldsymbol{\theta}_{t-1}) \mid \boldsymbol{R}_{\text{max}})||_{2^*}^2 \end{split}$$

where  $\alpha$ ,  $\beta$  are configurable hyper-parameters,  $\theta_{t-1}$  is the pretrained backbone model obtained from the previous DNN-ILT self-training iteration,  $R_{\text{nom}}$ ,  $R_{\text{min}}$ ,  $R_{\text{max}}$  are the nominal, minmum and maximum process conditions defined by the lithography simulation model, respectively (we omit the gradient for Equation (7) here due to the limited space, please refer [1] for details).

We use the DNN-ILT (based on  $\theta_{t-1}$ ) to generate the labels for the  $t^{\text{th}}$  iteration ourselves. This self-labelled dataset  $L_t = (\mathbb{Z}_t^{\text{d}}, \tilde{\mathbb{M}}_t^{\text{d}})$  is applied to pre-train a new backbone model  $\theta_t$  to minimize the pre-training loss (Figure 4(e))

$$L_{\text{pre\_train}} = ||\Phi(\mathcal{Z}_t^{\text{d}}|\boldsymbol{\theta}_t) - \tilde{\mathcal{M}}_t^{\text{d}}||_2^2 + \eta ||f(\Phi(\mathcal{Z}_t^{\text{d}}|\boldsymbol{\theta}_t) \mid \boldsymbol{R}_{\text{nom}}) - \mathcal{Z}_t^{\text{d}}||_2^2,$$

(8)

where  $\eta$  is a configurable hyper-parameter. As ILT is ill-posed, the second term in Equation (8) essentially introduces the domain-knowledge of the partially coherent imaging system and hereby guides  $\theta_t$  gradually converged towards a domain-specific direction.

#### Algorithm 1 Complete Self-training Paradigm for DNN-ILT

**Input:** Undisclosable layout pattern set  $\mathbb{Z}^{u}$ , lithography simulation model  $f(\cdot \mid R)$ .

**Output:** The best pre-trained DNN-ILT model  $\theta_{nt}^*$ .

1:

$$\mathbb{Z}^d \leftarrow \text{Pattern\_Generation}(\mathbb{Z}^u, c^2); \qquad \triangleright c^2 = 0.5$$

2: Split  $\mathbb{Z}^d$  into  $T$  batches, such that  $\mathbb{Z}^d = \bigcup_{i=1}^T \mathbb{Z}^d_i;$

- 3: Pre-train  $\theta_1$  with  $(\mathcal{Z}_1^d,\mathcal{Z}_1^d)$  to minimize Equation (9);

- 4: **for** Iteration t = 2,...,T **do**

- Initialize DNN-ILT with  $\theta_{t-1}$ ; 5:

- $\widetilde{\mathcal{M}}_{t}^{d} \leftarrow \text{DNN\_ILT\_Labeling}(\widetilde{\mathcal{Z}}_{t}^{d}, \theta_{t-1}); \triangleright \text{Equation}(7)$ 6:

- Pre-train  $\theta_t$  with  $(\mathcal{Z}_t^{\mathrm{d}}, \tilde{\mathcal{M}}_t^{\mathrm{d}})$  to minimize Equation (8); if  $\theta_t$  outperforms  $\theta_{\mathrm{pt}}^*$  in evaluation **then** 7:

- 8:

- $\theta_{\mathrm{pt}}^* \leftarrow \theta_t$ ;

- 10: **return** best pre-trained DNN-ILT model  $\theta_{nt}^*$ ;

Note that, in the first DNN-ILT self-training iteration, there is no  $\theta_0$  to conduct the on-neural-network ILT corrections for  $\mathcal{Z}_1^d$ , since we are completely building up the DNN-ILT from scratch with only unlabelled layout dataset  $\mathbb{Z}^d$ . Moreover, we observe that on-neuralnetwork ILT correction process (Equation (7)) cannot be directly applied on the network with common default initialization, i.e., initializing the network weights with random values under a certain distribution, because in practice, the ILT gradient will eliminate all on-mask shapes and fall into the trap of a local minimum. In order to avoid the local minimum trap, we enforce the forward prediction of  $\theta_1$  to be the first batch data itself, i.e.,  $\Phi(\mathcal{Z}_1^d|\theta_1) = \mathcal{Z}_1^d$ . As a result, the  $\theta_1$ 's pre-training step in the first round self-training is to minimize the self-reconstruction loss

$$L_{\text{self reconstruct}} = ||\Phi(\mathcal{Z}_1^{\text{d}}|\boldsymbol{\theta}_1) - \mathcal{Z}_1^{\text{d}}||_2^2.$$

(9)

Algorithm 1 depicts the complete flow of our proposed complete self-training paradigm.

### **EXPERIMENTAL RESULTS**

In this work, we explore how to build up an end-to-end on-neuralnetwork ILT correction framework from an undisclosable layout pattern set. The proposed flow is developed with PyTorch and CUDA, and tested on a Linux machine with a 2.2GHz Intel Xeon CPU and an Nvidia Titan V GPU.

#### 4.1 **Dataset**

4.1.1 Undisclosable layout pattern set. We obtain a layout pattern library from the authors of [12], which consists of 4300 instances of size  $2\mu m \times 2\mu m$  based on the design specifications for 32nm M1 layout topologies provided in the ICCAD 2013 mask optimization contest benchmark suite [15]. We regard it as the undisclosable layout pattern set  $\mathbb{Z}^{\mathbf{u}}$  in the following experiments.

4.1.2 Generated layout pattern set. Taking the undisclosable layout pattern set  $\mathbb{Z}^{\mathbf{u}}$  as inputs, we generated a new layout pattern set  $\mathbb{Z}^{\mathbf{d}}$ using the flow described in Section 2.2. For each layout pattern in  $\mathcal{Z}^u$ , we synthesized 4 new pattern topologies with a perturbation variance of  $c^2 = 0.5$ .

4.1.3 Test dataset. We use the ICCAD 2013 mask optimization contest benchmark suite (blind for training) and the corresponding lithography simulation engine lithosim\_v4 package [15] to evaluate the effectiveness of our proposed flow. The test benchmarks consists of ten  $2\mu m \times 2\mu m$  clips for 32nm M1 layout designs.

#### Effectiveness of Proposed Flow

The baseline flow [1] pre-trains its backbone model  $\theta_{\text{base}}$  directly with the training dataset ( $\mathbb{Z}^{u}$ ,  $\tilde{\mathbb{M}}^{u}$ ), where a conventional ILT tool [18] is used to synthesize the mask labels  $\tilde{M}^{u}$  for all the 4300 instances in Zu, and it takes approximately 10 days (> 240 hours) to finish the entire construction flow which includes data-preparation and model training.

For our proposed flow, we build up DNN-ILT directly with the unlabelled dataset Z<sup>d</sup> which contained 17200 newly generated layout patterns. We randomly split  $\mathbb{Z}^d$  into 4 batches, i.e.,  $\mathbb{Z}^d$  $\mathcal{Z}_1^d \bigcup \mathcal{Z}_2^d \bigcup \mathcal{Z}_3^d \bigcup \mathcal{Z}_4^d$ , and pre-train the backbone models  $\theta_1$ ,  $\theta_2$ ,  $\theta_3$ ,  $\theta_4$ following the pipeline described in Section 3.3. The entire pipeline synthesizes mask labels for around 13000  $2\mu m \times 2\mu m$  layout patterns (recall that  $\mathcal{I}_1^d$  does not require labelling) by DNN-ILT, which takes us approximately 3 days (< 72 hours) to finish the entire construction flow (includes data-preparation and model training).

To verify the effectiveness of our proposed flow, we optimize ten 32nm M1 layout masks in the ICCAD 2013 benchmark suite [15] based on the final pre-trained model  $\theta_{\mathrm{pt}}^* = \theta_3$  (i.e., performing DNN-ILT on  $\theta_3$ ) and compare the results with the baseline flow [1]. Quantitative results are listed in Table 2, where column "Runtime" lists end-to-end mask optimization (ILT) time for a given test layout. Columns " $L_2$ ", "PVB", "TAT" denote the squared  $L_2$  error, the process variation band, and the total turn around time for the entire flow construction (i.e., time to obtain the final DNN-ILT from scratch), respectively. We uses a consistent configuration for every test input, where the initial learning rate = 0.002, DNN-ILT iterations = 60,  $\alpha = 1.0$  and  $\beta = 1.0$  (Equation (7)). It can be observed that, in comparing to the state-of-the-art (SOTA) baseline flow [1], our flow achieves comparable performance in terms of "Runtime", "L<sub>2</sub>" and "PVB" metrics, while reduce 66% of the total turn around flow construction time. As mentioned in Section 1, an important feature of our flow is that, in the self-training paradigm, the end-to-end learning-based mask optimization framework is built up from the undiscloable layout pattern set Zu without actually "seeing" it. Unlike the baseline flow which directly uses ( $\mathcal{Z}^u$ ,  $\tilde{\mathcal{M}}^u$ ), none of these undiscloable layout patterns in  $\mathcal{Z}^{\mathbf{u}}$  is directly involved in the training of  $heta^*_{

m pt}$ , but the resulted DNN-ILT is still capable of conducting mask optimization for  $\mathbb{Z}^{u}$ .

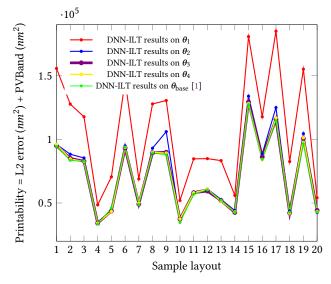

Here we further randomly pick up 20 layout patterns from  $\mathfrak{Z}^u$ to empirically verify the above statement. We conduct DNN-ILT corrections for the selected 20 sample layouts based on our pretrained models  $\{ heta_1, heta_2, heta_3, heta_4\}$  and the baseline model  $heta_{base}$  from [1]. Their printability scores ( $L_2$  + PVBand) are depicted in Figure 6. As expected, the printability score of  $\theta_1$  (red line) is not as good as that of  $\theta_{\text{base}}$  (green line), but the score gets significant improved on  $\theta_2$  (blue line) and gradually converged to baseline that was constructed with mask labels (green line) at  $\theta_3$  (purple line) and  $\theta_4$ (yellow line), while our approach does not need the provision of any input labels. The above empirical results indicate that our proposed

| Benchmarks |            | DNN-ILT with labelled real data [1] |              |                        |             | DNN-ILT by complete self-training (ours) |              |                        |             |

|------------|------------|-------------------------------------|--------------|------------------------|-------------|------------------------------------------|--------------|------------------------|-------------|

| ID         | Area (nm²) | Runtime (s)                         | $L_2 (nm^2)$ | PVB (nm <sup>2</sup> ) | TAT (hours) | Runtime (s)                              | $L_2 (nm^2)$ | PVB (nm <sup>2</sup> ) | TAT (hours) |

| case1      | 215344     | 13.57                               | 50795        | 63695                  | -           | 14.92                                    | 52583        | 62753                  | -           |

| case2      | 169280     | 14.37                               | 36969        | 60232                  | -           | 13.98                                    | 41471        | 56559                  | -           |

| case3      | 213504     | 9.72                                | 94447        | 85358                  | -           | 15.04                                    | 82360        | 111507                 | -           |

| case4      | 82560      | 10.40                               | 17420        | 32287                  | -           | 21.42                                    | 17597        | 32607                  | -           |

| case5      | 281958     | 10.04                               | 42337        | 65536                  | -           | 21.48                                    | 39405        | 64828                  | -           |

| case6      | 286234     | 11.11                               | 39601        | 59247                  | -           | 11.50                                    | 41535        | 56210                  | -           |

| case7      | 229149     | 9.67                                | 25424        | 50109                  | -           | 17.26                                    | 25884        | 50956                  | -           |

| case8      | 128544     | 11.81                               | 15588        | 25826                  | -           | 21.60                                    | 16562        | 26016                  | -           |

| case9      | 317581     | 9.68                                | 52304        | 68650                  | -           | 12.25                                    | 53319        | 67376                  | -           |

| case10     | 102400     | 11.46                               | 10153        | 22443                  | -           | 21.59                                    | 12199        | 21790                  | -           |

| Average    | -          | 11.18                               | 38504        | 53338                  | > 240       | 17.10                                    | 38292        | 55060                  | < 72        |

| Ratio      | -          | 1.00                                | 1.00         | 1.00                   | 1.00        | 1.53                                     | 0.99         | 1.03                   | < 0.33      |

Table 2: Mask Printability and Runtime Performance Comparison with the SOTA Method [1] on ICCAD13 Benchmark Suite

Figure 6: The DNN-ILT correction results of 20 sample layouts based on the pre-trained models  $\{\theta_1, \theta_2, \theta_3, \theta_4\}$  and the baseline model  $\theta_{\text{base}}$  [1], where the printability score =  $L_2$  error  $(nm^2)$  + PVBand  $(nm^2)$ .

flow can achieve fast convergence (e.g., from  $\theta_1$  to  $\theta_4$ ) to good performance by this iterative self-training approach even without any input mask labels. Meanwhile, our complete self-training can efficiently capture the useful characteristics of undisclosable layouts in a secure manner.

#### 5 CONCLUSION

In this paper<sup>1</sup>, we present a unified self-training paradigm to build up an end-to-end mask optimization framework from undisclosable layout patterns. Quantitative results verified its effectiveness. The presented flow can be easily extended to rigorous simulation environment in fab and vendor for their internal use. Future works would include detailed analysis on the reversibility of generated patterns and the empirical risk of the self-training flow.

#### **REFERENCES**

- B. Jiang, L. Liu, Y. Ma, H. Zhang, B. Yu, and E. F. Y. Young, "Neural-ilt: Migrating ilt to neural networks for mask printability and complexity co-optimization," in Proceedings of the 39th International Conference on Computer-Aided Design, 2020.

- [2] C. Mack, Fundamental Principles of Optical Lithography: The Science of Microfabrication. John Wiley & Sons, 2008.

- [3] R. Pearman, J. Ungar, N. Shirali, A. Shendre, M. Niewczas, L. Pang, and A. Fujimura, "How curvilinear mask patterning will enhance the euv process window: a study using rigorous wafer+ mask dual simulation," in *Proceedings of SPIE*, vol. 11178, 2019.

- [4] K. Hooker, B. Kuechler, A. Kazarian, G. Xiao, and K. Lucas, "ILT optimization of EUV masks for sub-7nm lithography," in *Proceedings of SPIE*, vol. 10446, 2017.

- [5] M. Yeung and E. Barouch, "Development of fast rigorous simulator for large-area EUV lithography simulation," in *Extreme Ultraviolet (EUV) Lithography X*, vol. 10957, International Society for Optics and Photonics. SPIE, 2019, pp. 286 – 295.

- [6] W. Ye, M. B. Alawieh, Y. Watanabe, S. Nojima, Y. Lin, and D. Z. Pan, "Tempo: Fast mask topography effect modeling with deep learning," in ACM International Symposium on Physical Design (ISPD), 2020, p. 127–134.

- [7] H. Tanabe, S. Sato, and A. Takahashi, "Fast 3D lithography simulation by convolutional neural network: POC study," in *Photomask Technology 2020*, vol. 11518.

SPIE, 2020, pp. 1 7.

- [8] Y. Lin, M. Li, Y. Watanabe, T. Kimura, T. Matsunawa, S. Nojima, and D. Z. Pan, "Data efficient lithography modeling with transfer learning and active data selection," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, 2019.

- [9] G. Chen, W. Chen, Y. Ma, H. Yang, and B. Yu, "Damo: Deep agile mask optimization for full chip scale," arXiv preprint arXiv:2008.00806, 2020.

- [10] P. Liu, "Mask synthesis using machine learning software and hardware platforms," in *Optical Microlithography XXXIII*, vol. 11327. International Society for Optics and Photonics, 2020, p. 1132707.

- [11] H. Geng, H. Yang, L. Zhang, J. Miao, F. Yang, X. Zeng, and B. Yu, "Hotspot detection via attention-based deep layout metric learning," in IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2020.

- [12] H. Yang, S. Li, Y. Ma, B. Yu, and E. F. Young, "GAN-OPC: Mask optimization with lithography-guided generative adversarial nets," in ACM/IEEE Design Automation Conference (DAC), 2018, pp. 131:1–131:6.

- [13] W. Zhong, S. Hu, Y. Ma, H. Yang, X. Ma, and B. Yu, "Deep learning-driven simultaneous layout decomposition and mask optimization," in ACM/IEEE Design Automation Conference (DAC), 2020.

- [14] Y. Ma, W. Zhong, S. Hu, J. Gao, J. Kuang, J. Miao, and B. Yu, "A unified framework for simultaneous layout decomposition and mask optimization," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, pp. 1–1, 2020.

- [15] S. Banerjee, Z. Li, and S. R. Nassif, "ICCAD-2013 CAD contest in mask optimization and benchmark suite," in *IEEE/ACM International Conference on Computer-Aided Design (ICCAD)*, 2013, pp. 271–274.

[16] X. Zhang, J. Shiely, and E. F. Y. Young, "Layout pattern generation and legaliza-

- [16] X. Zhang, J. Shiely, and E. F. Y. Young, "Layout pattern generation and legalization with generative learning models," in *Proceedings of the 39th International* Conference on Computer-Aided Design, 2020.

- [17] I. Triguero, S. García, and F. Herrera, "Self-labeled techniques for semi-supervised learning: taxonomy, software and empirical study," *Knowledge and Information* systems, vol. 42, no. 2, pp. 245–284, 2015.

- [18] J.-R. Gao, X. Xu, B. Yu, and D. Z. Pan, "MOSAIC: Mask optimizing solution with process window aware inverse correction," in ACM/IEEE Design Automation Conference (DAC), 2014, pp. 52:1–52:6.

<sup>&</sup>lt;sup>1</sup>The work described in this paper was partially supported by a grant from the Research Grants Council of the Hong Kong Special Administrative Region, China (Project No. CUHK14209320).